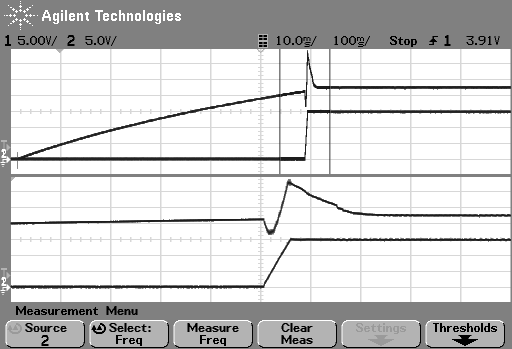

Below, a proper startup-sequence is documented. It was captured while the capacitor on the CS pin was fairly high (1 nF, reference: e2e.ti.com/.../522410).

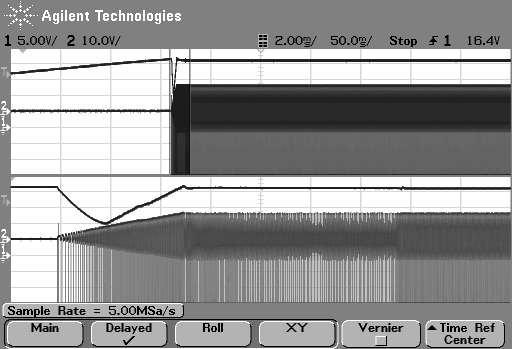

BTW: a fairly high overshoot in the VDD voltage (top trace, approx. 35V) occurs here. The bottom trace shows a 16V secondary voltage (bulk cap: 220 uF, operating voltage 16V).

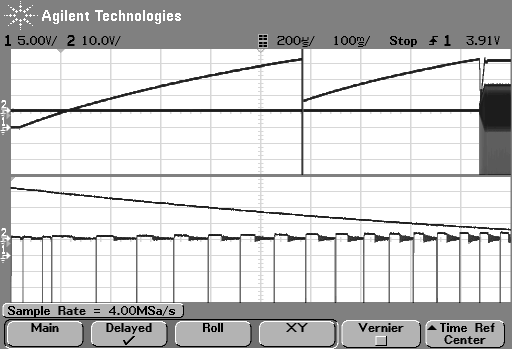

Next capture is without 1 nF on the CS pin (and Vdd capacitor 330 nF) Startup time would be 600 ms without the failed charge in the middle:

After the first Vdd-chargeup, Vdd goes back to undervoltage lockout. The second "try" goes OK. In this case, not the secondary rectified voltage is captured, but instead the voltage on the secondary winding. It can be seen that the switching frequency start quite low, and increases with increasing secondary voltage??

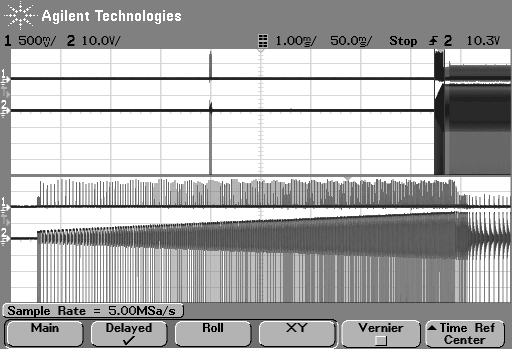

Next, more detail is given. Here, not Vdd is shown, but the voltage on the CS pin (with 100 pF). In the middle, a first PWM start did not transfer enough energy before Vdd touches undervoltage lockout.

The top trace shows that the CS ramps up to approx. 750 mV (with some variation mainly due to 5MSPS sample rate - zooming has proven that what you see here is truly the top of each current ramp, not any spike). This is Okay. It can clearly be seen that the frequency starts low and then increases. Why is the frequency not at least 44 kHz right from the start? The output capacitor would charge much faster!

Momentarily I'd suggest to increase the Vdd capacitor while also decreasing the resistance of the start-up ladder in order to keep start-up time clearly below one second OR the output bulk capacitor is decreased to 100 uF (which - at 16V would constitute the very same energy as 1000uF @ 16V

But of course it would be better to have 44 kHz right from the start. Any hint about this?