Im driving EPC2032's from the LM5113, and more often than i'd like, Im having fet failures. The project is a motor drive, so essentially its acting as a synchronous buck converter most of the time. While some failures seemed to be related to soldering (too much heat, or too long) and other failures due to my own accidents, I'm still having failures that I can't track down the real cause. All of the failures until the most recent one did not damage the gate driver IC. I give this background, because, I really have low certainty in any of my theories about what's going wrong.

My board design is essentially a rip-off of the EPC9013 demo board:

Except im using the EPC2032 instead of the 2001. Also, my board is 6 layer for increased current handling, and im trying to stack 4 of the boards in parallel to handle higher currents up to 200A.

So on this last failure, all of the high-side fets were nearly blown off the PCB, while all of the low-side fets measure perfectly fine (and, indeed, work fine now that the bad parts were replaced). The high-side gate driver shows that there was a failure in the isolation section, as the driver output measures 20 ohms to Vss. My suspicion is that the gate driver failed first, and killed all the high-side fets by applying -Vsupply (50V) to the gates essentially. Input voltage to the bridge was 50V, and i have not seen any overshoot in excess of 10V on the output.

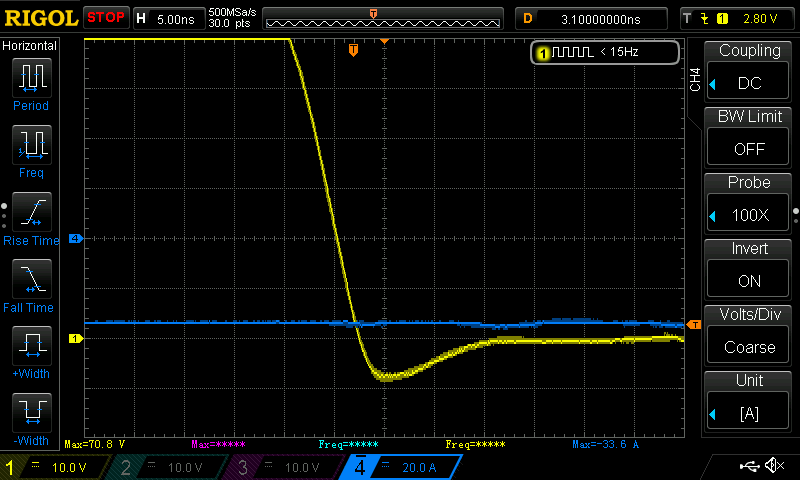

When i look at the HS pin vs VSS i see up to -8V excursions (lasting 5nS or so). Matching my over-shoot and ringing frequency (~250MHz) to a spice sim suggests i have about 100pH of total power loop inductance. I don't know that i could do any better.

I tested a new driver to destruction and found that it took -15VDC from HS to VSS to kill it (while there was 5V on VCC to VSS). The resulting breakdown gave a similar low resistance from the high-side output to Vss as the gate driver that failed under use.

When i probe the EPC9013 demo board i see the same -8V excursion (70VDC input, switching 35A). I am of course, probing as close to the IC pins as possible and not using the long ground lead on the probe. The scope capture shows HS-VSS on channel 1 (yellow) and load current on channel 4 (blue).

So, how serious is this transient? I figure it can't be too bad, or else EPC probably wouldn't get away with it. Any insight into how sensitive, or how predictable (or unpredictable) damaging the isolation well is would be useful for me.