Hi,

I have a question about TPS650842 in Intel braswell platform(N3010)

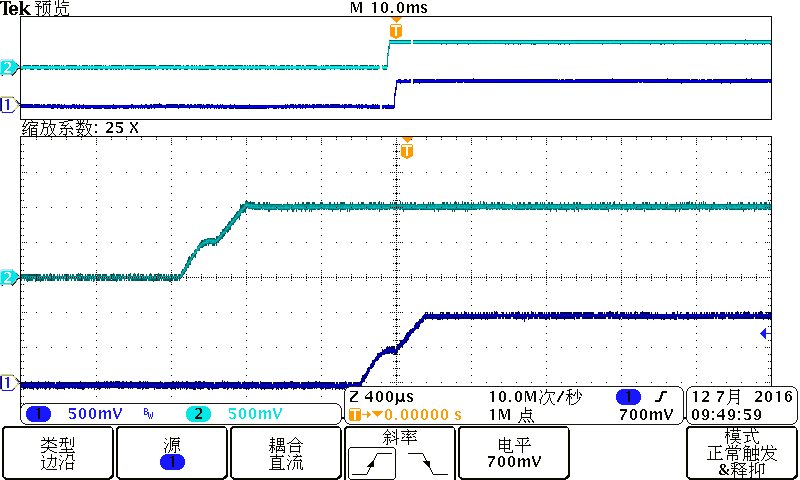

1. In the cold boot sequence, every voltage rail is right, and the SOC(N3010)pull up the SLP_S4_N & SLP_S3_N, make the system into S3 mode. But after TPS650842 pull the COREPWROK & VCCAPWROK , the SOC PLTRST_N still low, the system cannot power up. The sch is in attach file. please help , thanks!x86_n3000_core_0603no.pdf