I am having trouble with my fault timer.

I am using the LM5069-1 as a circuit breaker and an inrush current controller on a 24V rail, with a load that has 600uF of capacitance.

i have selected 1.0uF (10%) for Ct. the 85uA fault timer current can be 51uA to 120uA. and the timer threshold voltage can be 3.76V to 4.16V. which should result in at fault time out of ≈ 30ms - 90ms.

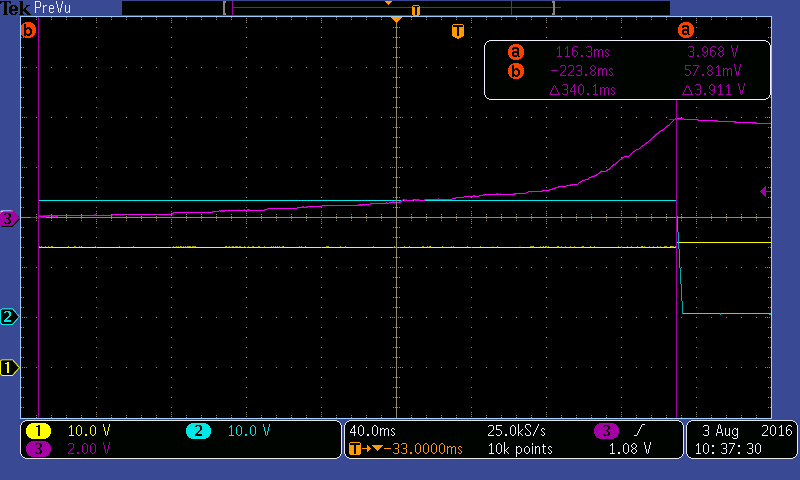

in lab i am testing this and i am measuring much longer than that. 340ms! what am i missing here?