Customer's question on the datasheet diagrams for application diagram and sequence timings.

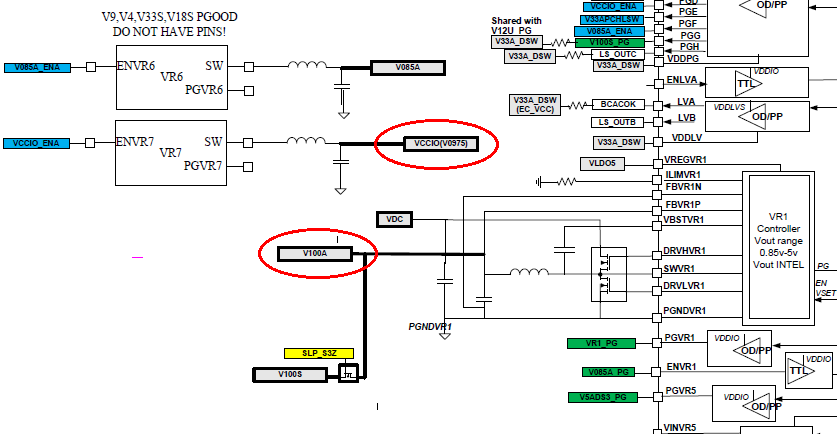

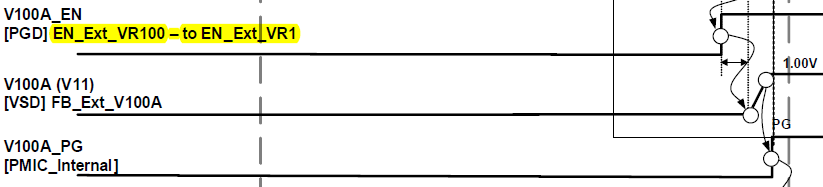

From the system block diagram of TPS650832, the V100A is the output of internal VR1, and VCCIO is the output from external VR7.

But Timing Diagram shows the V100A is Enabled by External VR1, and VCCIO is enabled by internal VR1, this is confused to customer. Is this a typo error?

Or could you please help to add some comments on that? Thanks!

V100A

VCCIO