Hello

I've to redesign old DC/DC modules containing Simple-Switcher controller. The goal is to achive a much better efficiency.

The device work properly so far, except I've problems with the HF noise on Vout. Due to the layout, I think.

I've compared it with the eval board, but haven't any idea.

Could some one look over it and give me some hints?

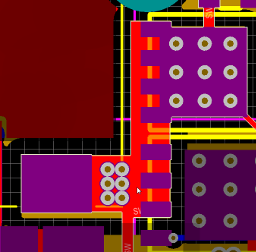

Schematic:

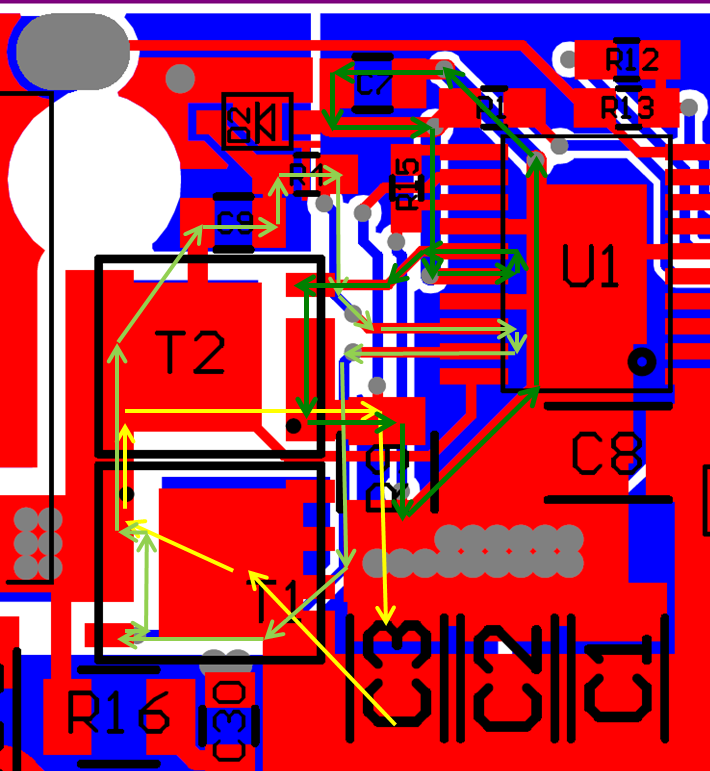

Layout:

Some waveforms: