Hi,

Here are the Power rail monitoring and corresponding GPO Enable for the regulators.

| Pin Name | Pin# | Monitoring Voltage |

| MON1 | 1 | +5v |

| MON2 | 2 | +1.8v |

| MON3 | 38 | +3.3V |

| MON4 | 39 | +2.5V |

| MON5 | 40 | +1.8VD |

| MON6 | 41 | +1.0V |

| MON7 | 42 | +1.35V |

| MON8 | 45 | VTT |

| MON9 | 46 | S1VDD |

| MON10 | 48 | +1.5V |

| MON11 | 37 | +3.3VD |

| Pin Name | Pin# | Net Name | Enabling Voltage Rails | Power On Seq | Power Off Seq | ||

| GPIO1 | 4 | P_ENABLE1 | +1.8v | +2.5V | +3.3V | 1st | 1st |

| GPIO2 | 5 | P_ENABLE2 | +1.0V | 2nd | 2nd | ||

| GPIO3 | 6 | P_ENABLE3 | +1.5V | S1VDD | |||

| GPIO4 | 7 | P_ENABLE4 | VTT | +1.35V | 3rd | 1st | |

| GPIO5 | 10 | P_ENABLE5 | +1.8VD | +2.5VD | 4th | ||

| GPIO6 | 11 | P_ENABLE6 | +3.3VD | 5th | |||

1. We Implemented the power on sequence as per the above order, through Auto Enable Option. We are not finding any way to implement the power down sequence.

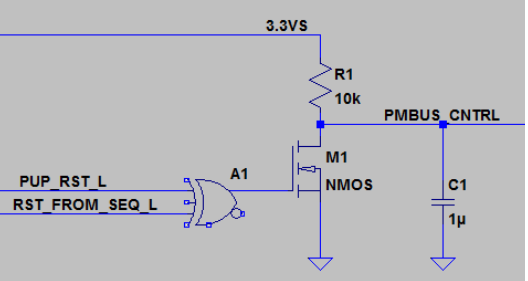

2. We have one GPO configured in UCD , which will send out a high when all power rails are good. This acts as as Power Up reset signal goes to CPLD. After CPLD receives this it will send out reset signals to different devices in order to bring them out of reset.

3. After CPLD programming is over, CPLD will send out a signal to UCD (GPI) to initiate the power cycle. This will decide the power down sequence.

I could see other threats which raised similar issues. Give some insight how to implement this Power on & Off sequence.

Regards,

Felix.