Hi there,

We use TPS73001 to generate 2.5V from 5V input, 50mA.

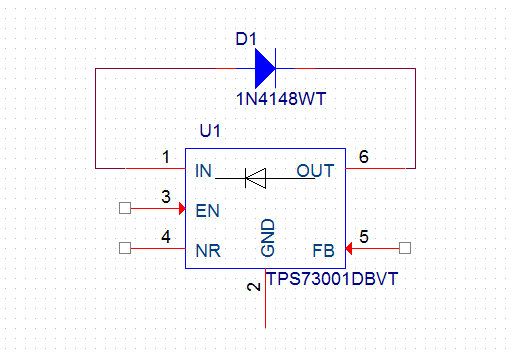

As reverse current is not internally limited(Section 8.1.5 of datasheet), how could we implement external circuit to prevent/limit the reverse current, during power down?

Could you please suggest some practical demo circuit on this?

Thanks.