Hi team,

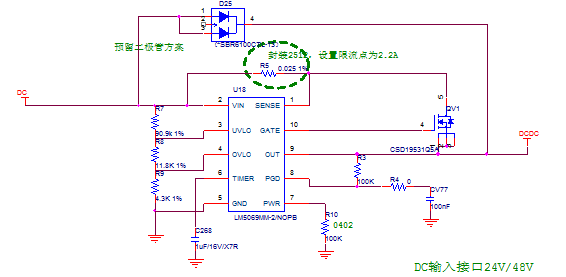

My customer wants to use LM5069 in their system, which is 24V or 48V input compatible. The schematic as below:

the output cap is 680uF, which is the input of a DC/DC (LM5576, 24V/48V to 12V/1A)

the MOSFET is CSD19534Q5A, instead of 19531

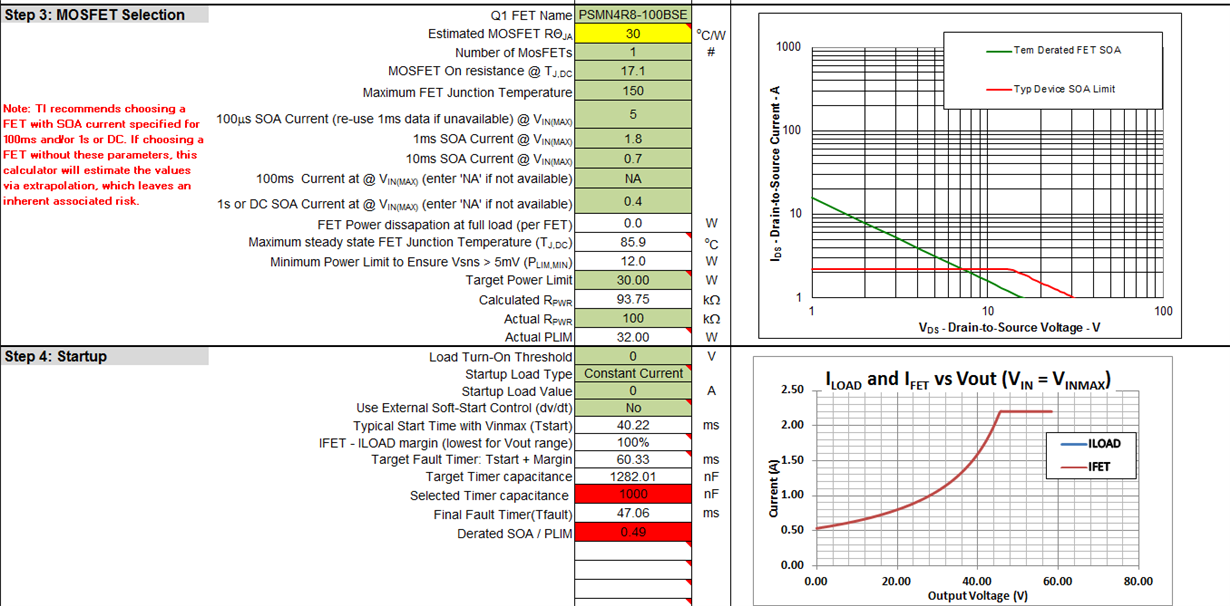

I used the calculate tool and found some result has high risk. I attached the excel sheet for your reference.

4786.Copy of LM5069_Design_Calculator_REV_B.xlsx

regarding the result, I have some questions:

1. what does the green trace/red trace in SOA figure stand for?

2. could you please explain the start up figure? If the output voltage already reaches 48V, why does the current clamped to 2.2A? the max load current was set as 1.3A.

3. How does the tool calculate the typical start time and target fault timer?

4. For customer's application, how to determine the power limit and timer cap? could you please suggust a proper value?

thanks:)

BR,

Mike