Hi all,

This is from Taiwan TI sales team in charge of Delta Electronics.Our Delta customers have some questions regarding the hysteresis design of UCC28220.

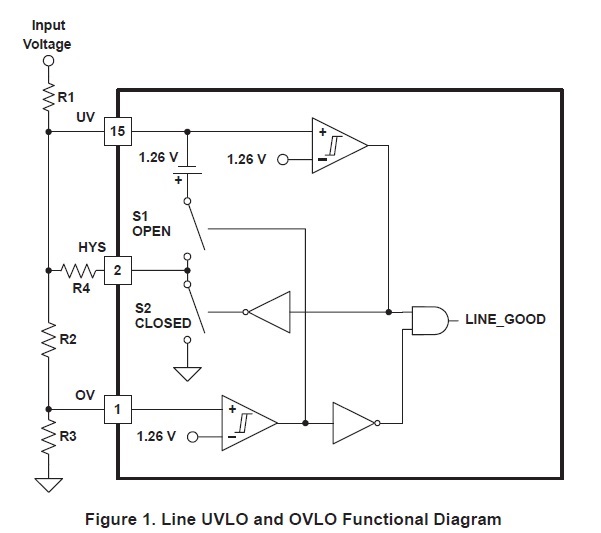

The function block for the UVLO & OVLO is a bit confusing, please help us to clarify the states of the switch.

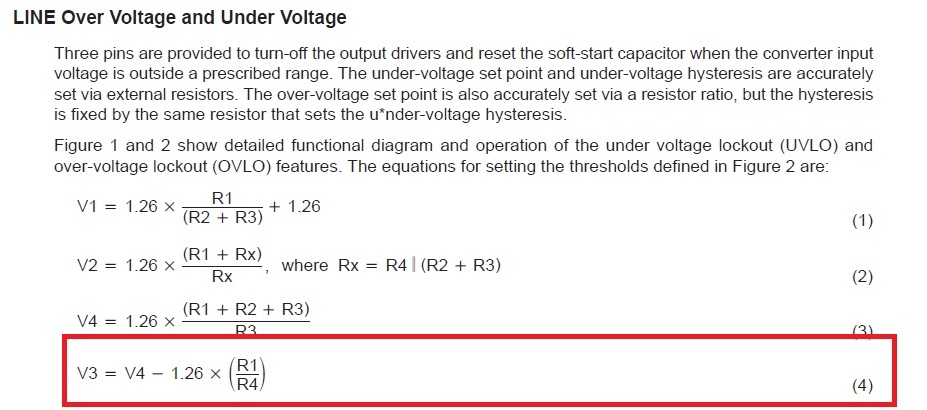

If the control signal is either HIGH or LOW, what would be the state of switches? Based on Equations 1 - 4, it seems the switch is CLOSED when control signal from the comparator output is HIGH; and switch is OPEN when control signal is LOW. (Please correct me if I am wrong)

If the above statement was correct, they wish to know how Equation 4 for calculating V3 (OV VTL) was derived?

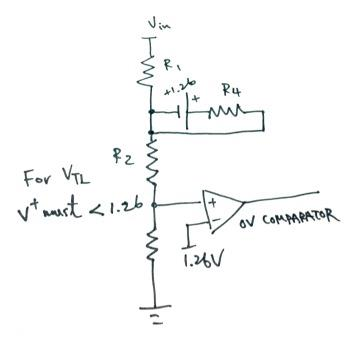

When the device enters OV state, S1 should be CLOSED and S2 should be OPEN. The equivalent hysteresis circuit should look like:

which does not make a lot of sense, how does R4 effect the voltage across non-inverting input of the OV comparator (OV pin)?

Thank you very much.

Best Regards,

Wei-Hao Chen

Analog GAE