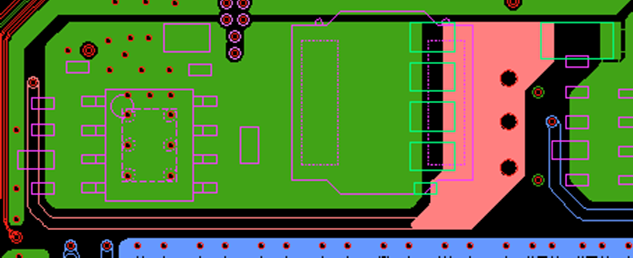

Customer is using TPS54327, but layout found below point. (5Vin⇒1Vout, 400mA)

※Pink is 1st layer, green is 8th layer.

・1st layer's inductor and 8th layer's output capacitor are overlap (right behind).

・In general, in the case of 2 layer board have possible of noise.

⇒If 8 layer board and setting GND layer(2nd layer), noise problem is eliminate, is it correct?

Best regards,

Satoshi