hi team

LM2936-Q1-5.0 need at least 10uF with ESR 0.3Ohm ~ 8Ohm for stability.

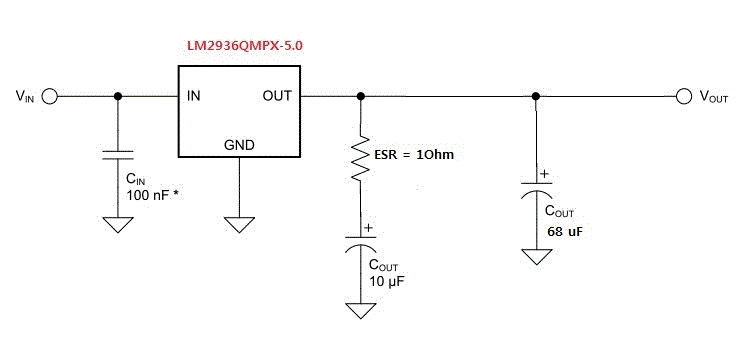

BTW,,, customer made the board as below; 10uF with External ESR = 1 ohm, and 68uF with no external ESR.

it seems the board will make unstable.

my questions are...

[Q1] what is max cout with ESR 0.3Ohm ~ 8Ohm for safe stability for LM2936-Q1-5.0 ?

[Q2] such customer configuration(10uF with External ESR = 1 ohm, and 68uF with no external ESR) can meet stability ?

if not, tell me why and how to improve the stability ?