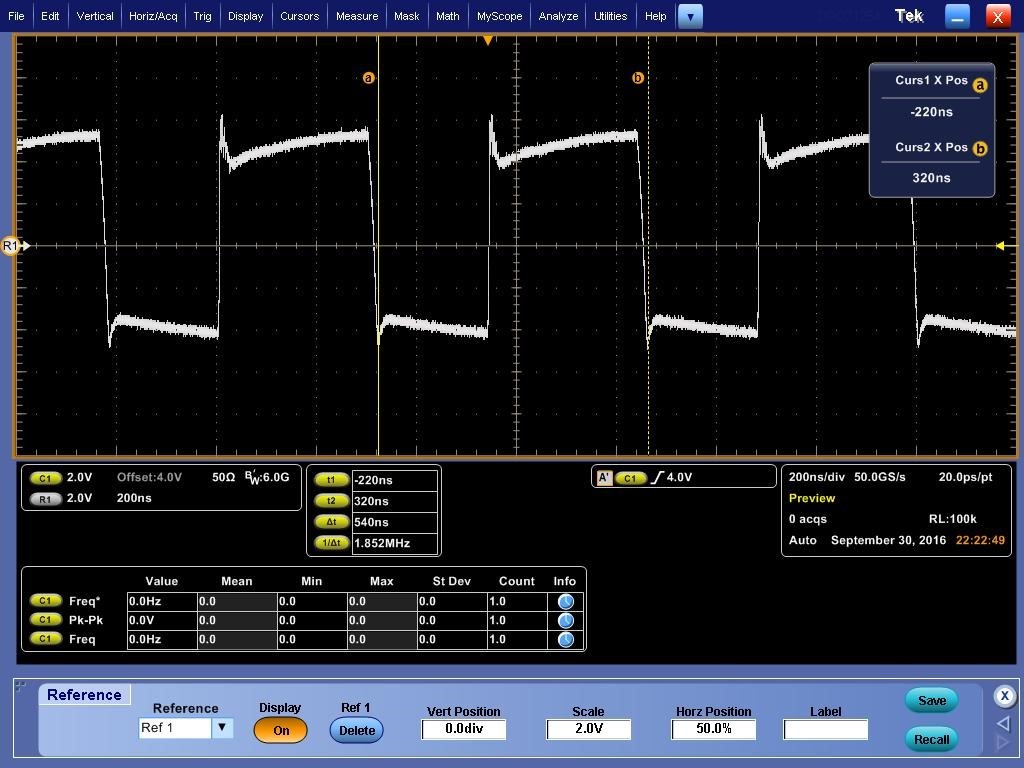

We failed ECE Reg 10 for Radiated Emissions in Europe by 4 dB @ 258 MHz. After probing around, most of the radiation was coming from the TPS54341 switcher. The solution was decreasing the DC switching frequency from 2.5 MHz to 2 MHz and adding a snubber. In the lab, this dropped the radiated emissions by 7 dB @ 258 MHz. Resending the boards for testing, they failed again, this time the test was EN 300 440-1 clause 7.3 and they failed by 9.2 dB @ 224 MHz. Has anyone else had trouble with the TPS54341 pass radiated emissions for EU? Does anyone have an idea how we can solve this?

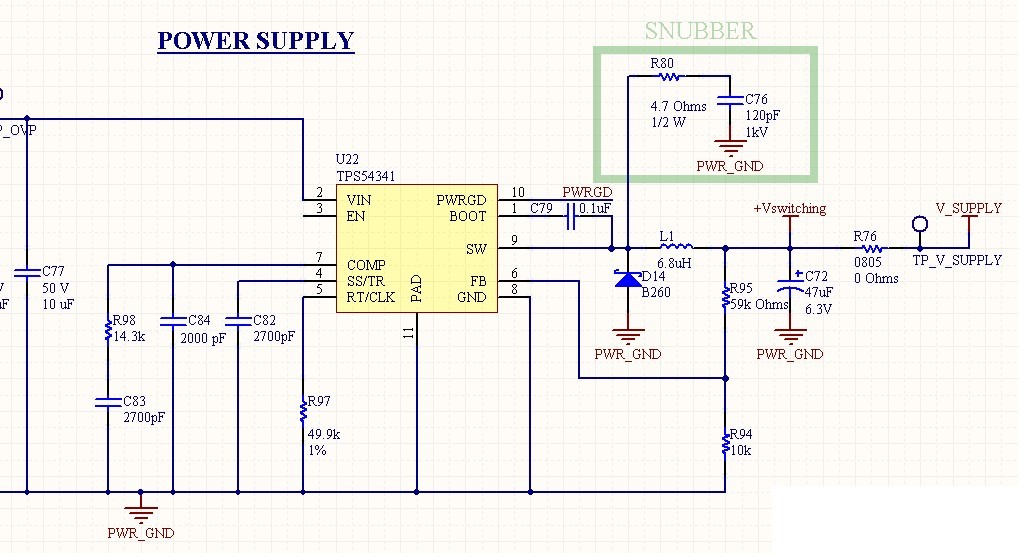

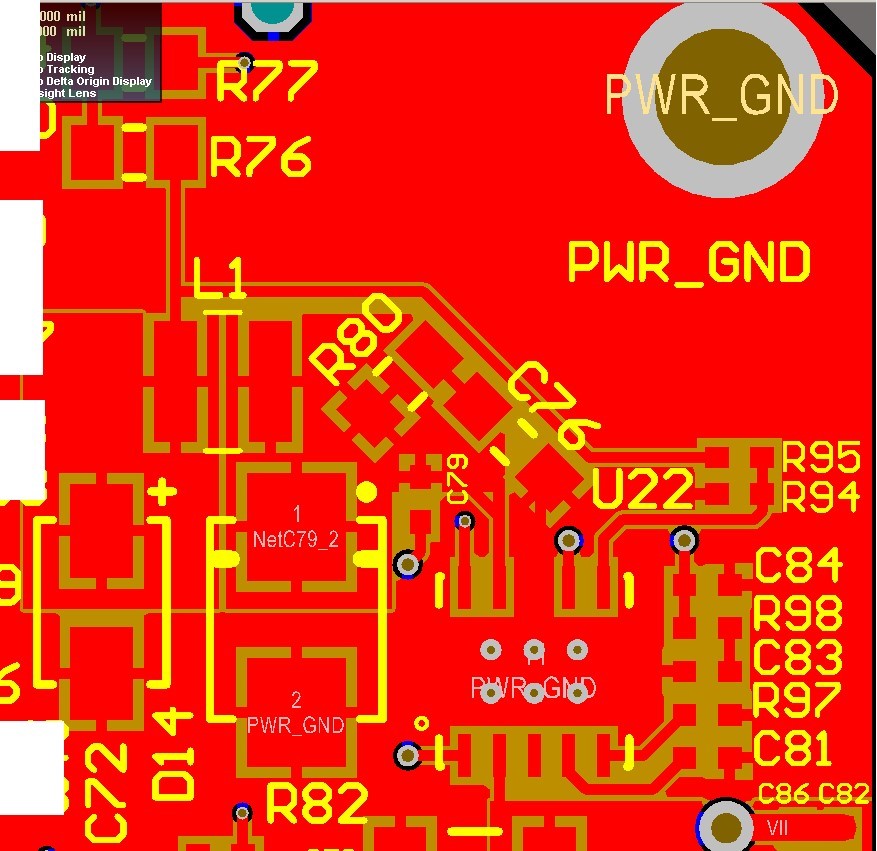

Setup for TPS54341:

Switching frequency: 2 MHz

Snubber (placed before output unductor): 4.7 Ohms in series with 120 pF

Vin (average) = 12 V

Output Inductor: 6.8 uH (SRN3015-6R8M)

Output Cap (after output inductor): 47 uF

Other helpful information:

The unit passed FCC Part 15.209 @ lower emission testing