Hi guys,

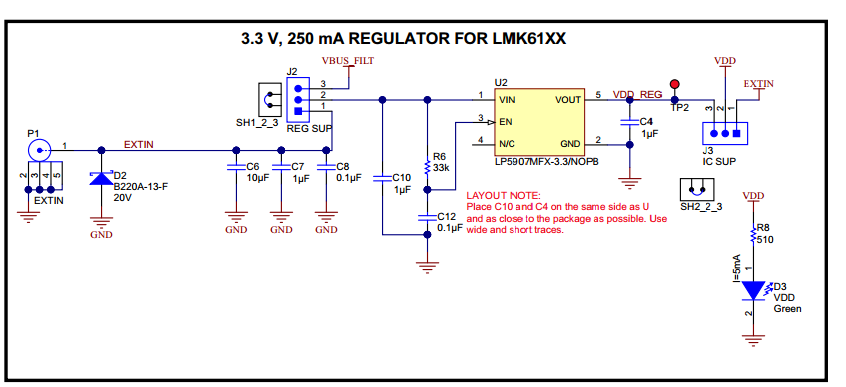

I have a question regarding the LP5907 on the LMK61e2 EVM. If I want to power the OSC device via external power (as opposed to usb), but I don’t have an sma connector for power, can I leave J2 floating to disable the LP5907 LDO and apply 3.3V to VDD_REG?

Basically I am wondering if there would be an issue applying 3.3V to Vout of the LDO when the LDO is powered down. Looking at the DS for the LP5907, if enable (EN) is low and the LDO is fully disabled, automatic output discharge is activated. So we have a 230Ohm pull down giving us a fairly low impedance path to ground. So I am thinking VDD_Reg cannot be used as an external input to power LMK61e2. Let me know if this is correct.