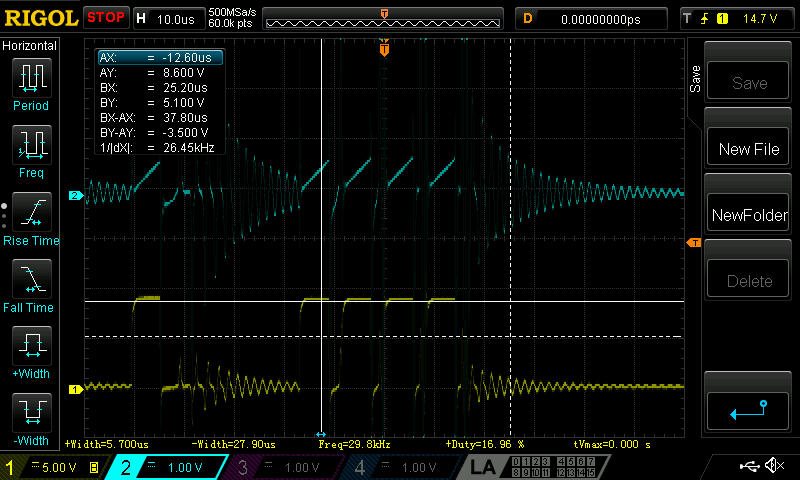

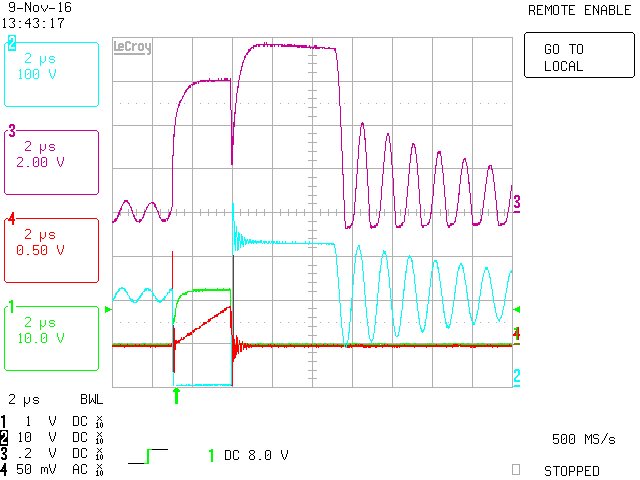

I have a 550uH 8:1:1 transformer with 10% max leakage, Rp=3.92K, Ra=24.3K, Rb=47.5K and Rcs=0.4

output target is 12-15V (not picky since it replaces an unreg supply) at 36W (also not critical)

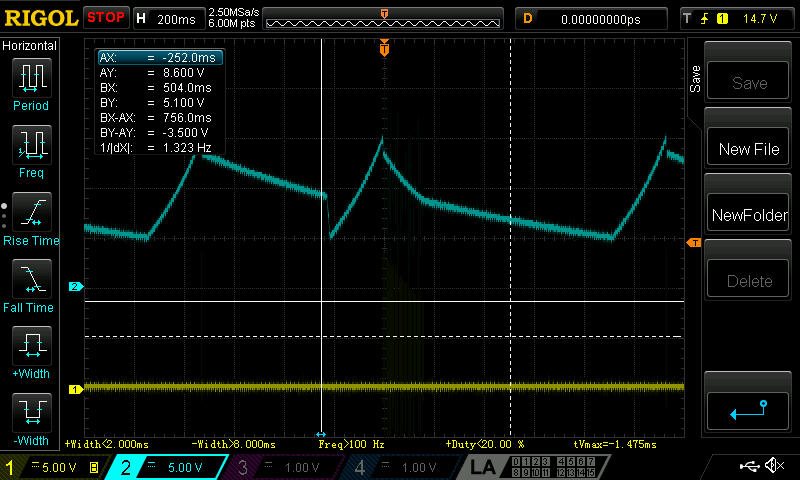

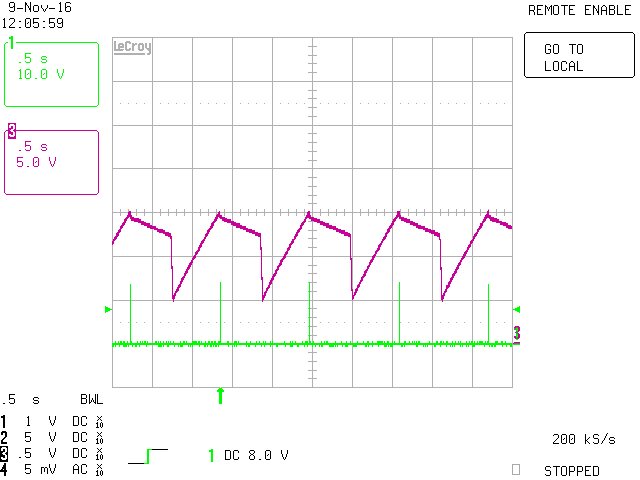

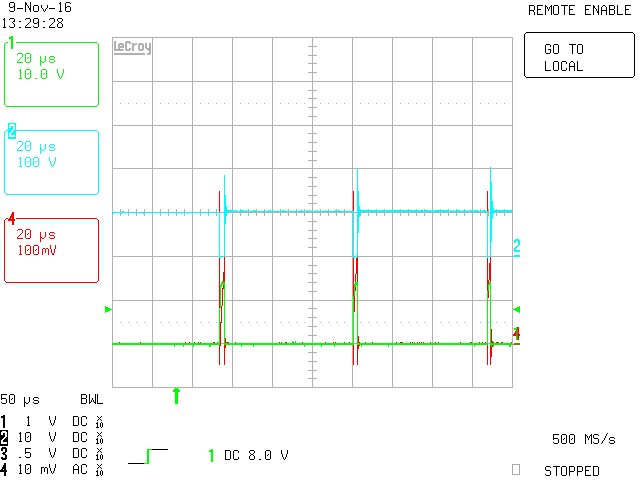

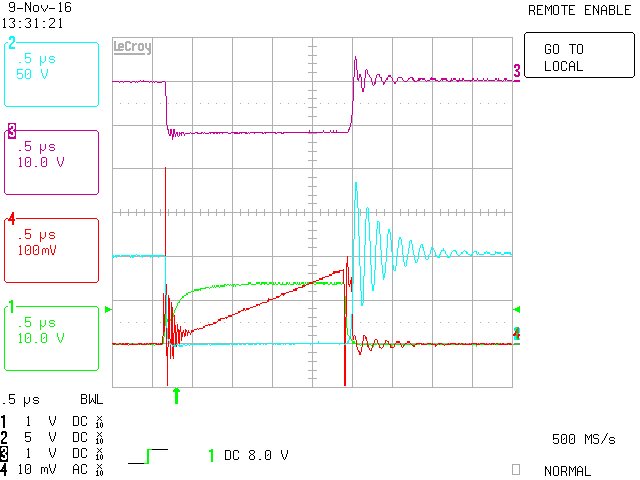

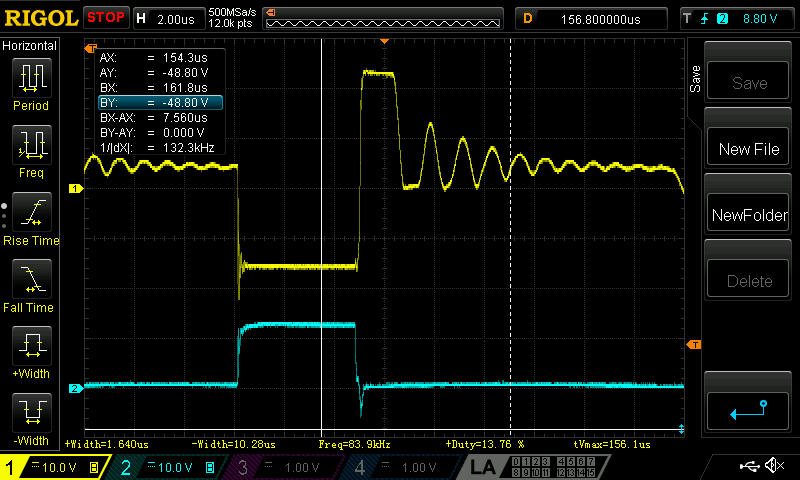

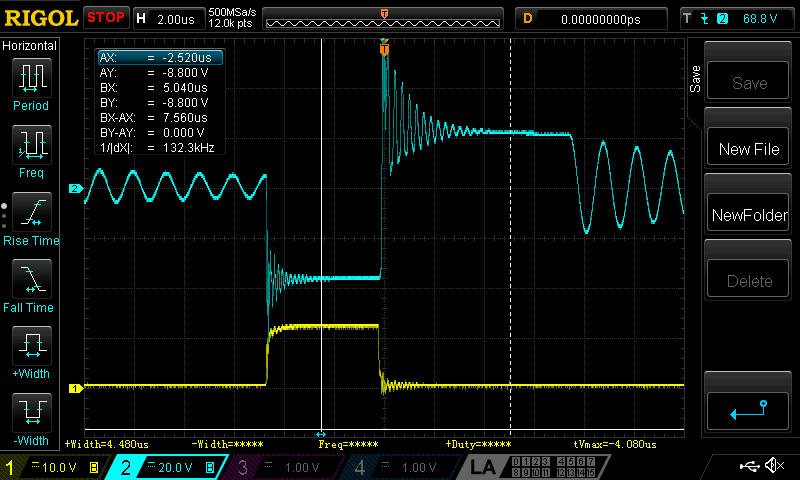

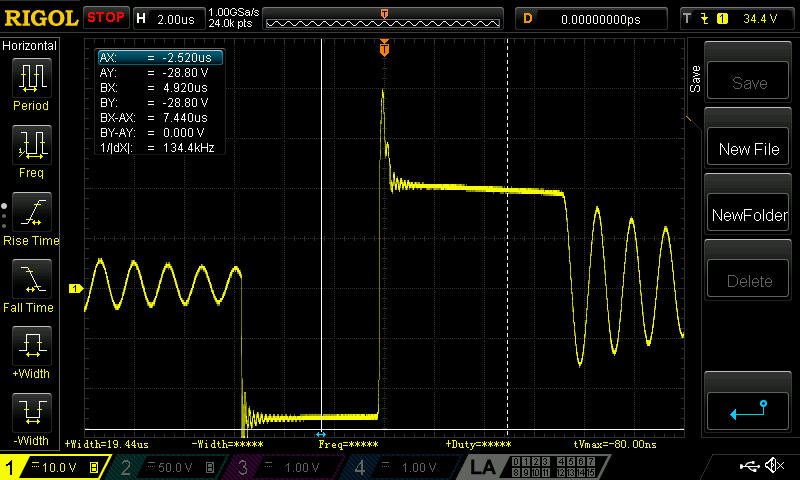

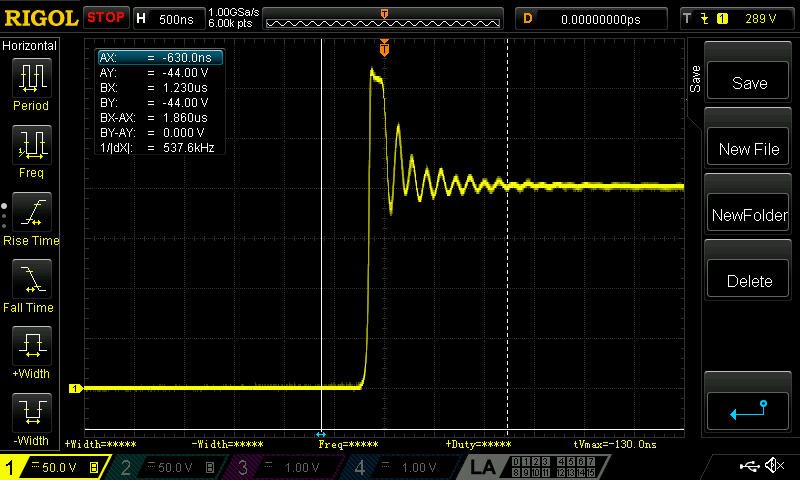

the chip error code varies between VDD low and Vbus low at 150V bus under no and low load

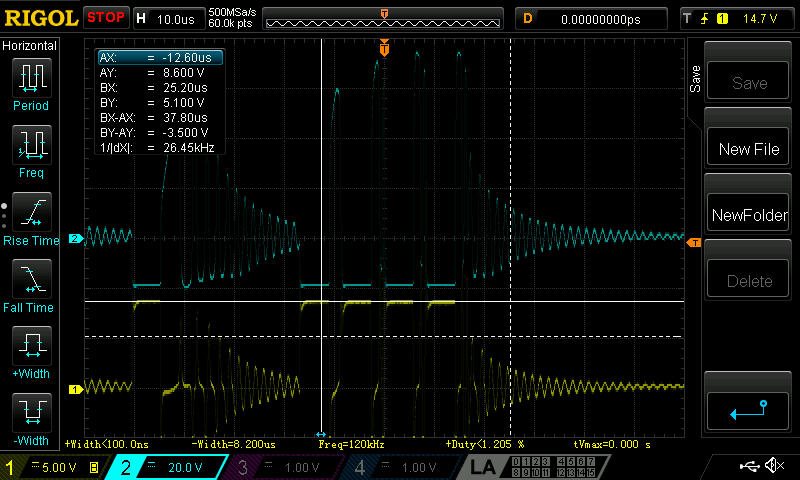

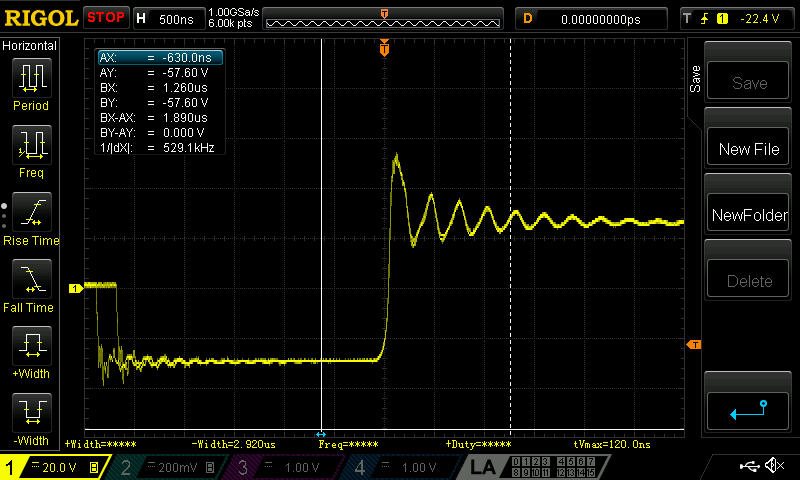

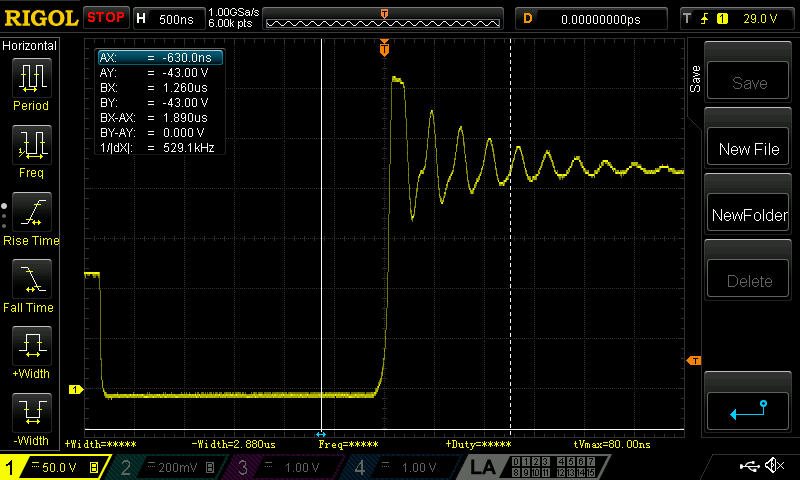

seems like the only things amiss from the forums is bringing it up slow and a standard RC clamper

any thoughts while i try to rig a 200V clamp?