Hi,

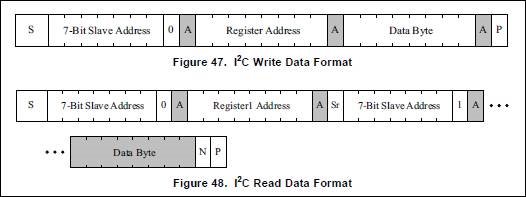

As the datasheet of TPS65273V , I2C read data sequence is as below.

START => Device Address => 0(Write) => Register Address => Repeated start => Device Address => 1(Read) => Data => STOP

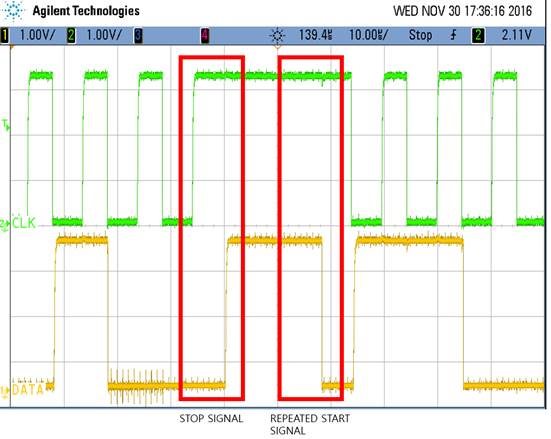

However, in case of our application, the STOP Signal exist just before the Repeated start signal.

SRART => Device Address => 0(Write) => Register Address => STOP => Repeated start => Device Address => 1(Read) => Data => STOP

I think if CPU send STOP SIGNAL in the middle of sequence, the communication is broken.

But I2C communication with TPS65273V is mostly work well, and abnormal status shown intermittently.

For your information, the other vendor's devices which communicate with my SET completely missed connection due to the stop signal.

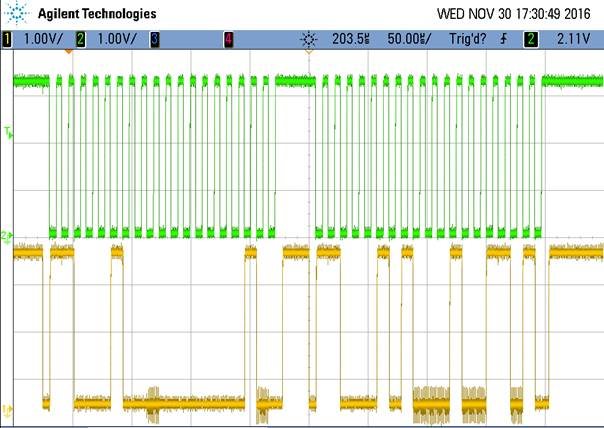

below waveform is when read the TPS65273V(ADDRESS 0x62H) Vout2_SEL(0x01H).

To sum up, my question is as below.

1. Is there any problem for TPS65273V I2C communication if there is STOP Signal in front of Repeated start signal?

2. If there's some problem, why the bulk of traffic is normal and communication error happens sometimes?

Please look through above questions, and give us a reply.

thanks,

TS