Hi,

Customer found some unexpected UVLO behavior as described below. Please let us know what can be checked as a next step.

- Customer board shall be able to supplied by either batter or AC adapter.

- From the beginning, board is powered up correctly by battery insertion.

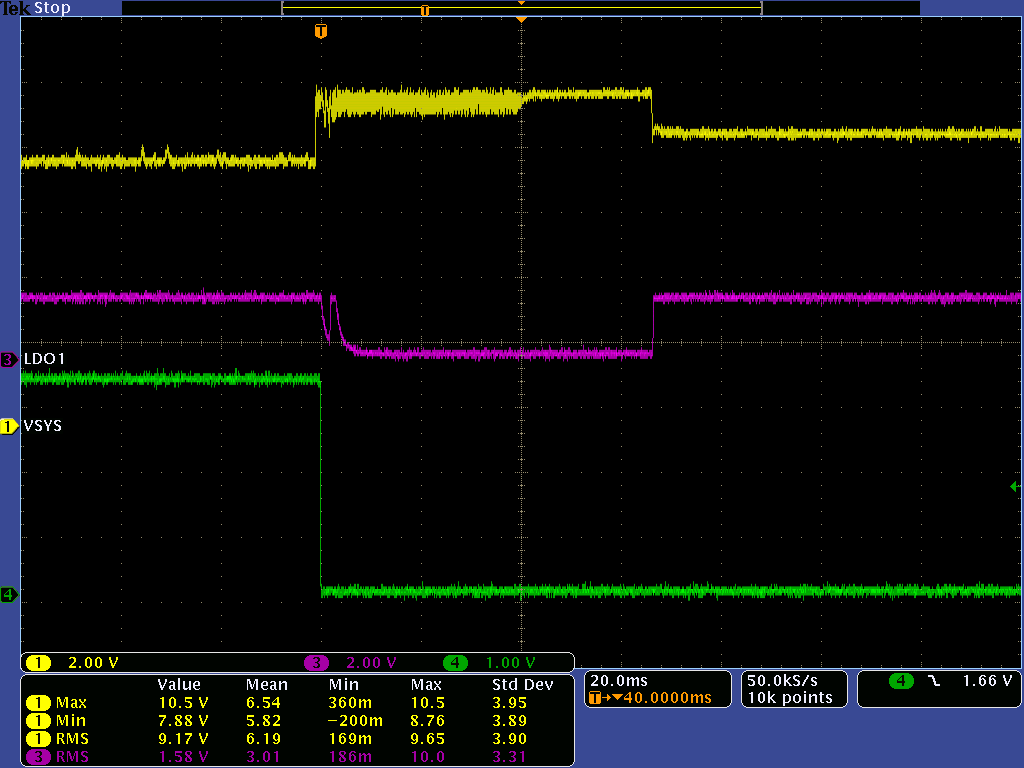

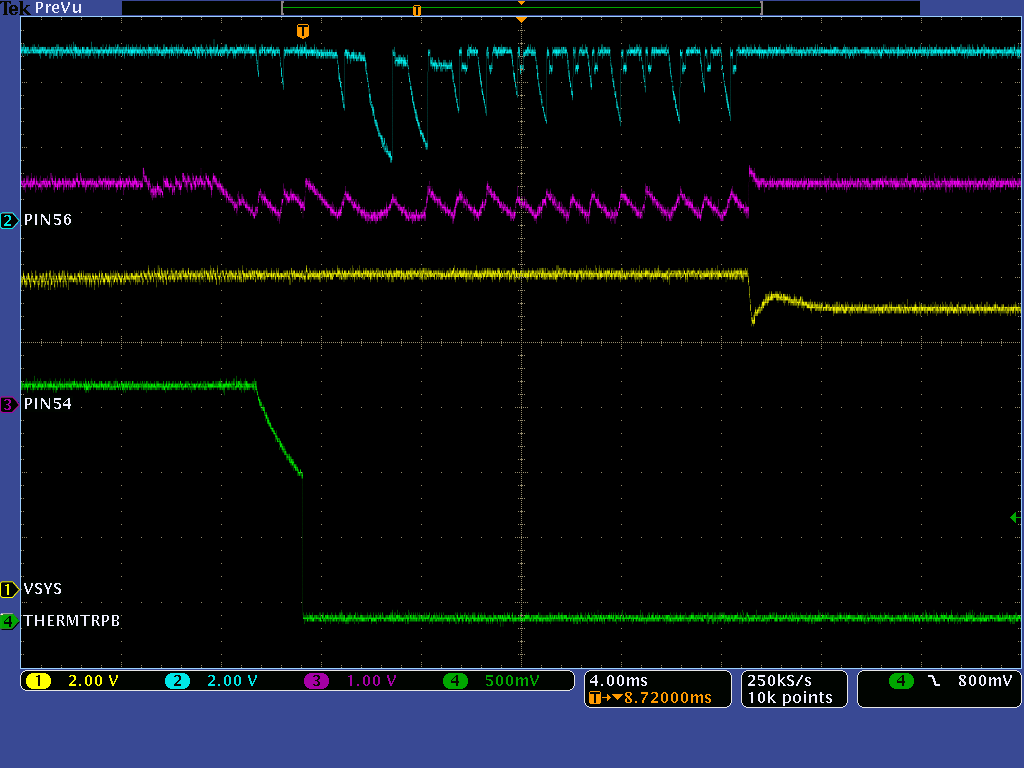

- Then, customer plug-in AC adapter and immediately found system is unexpetedly turned off as described below. (Only on some of the boards.)

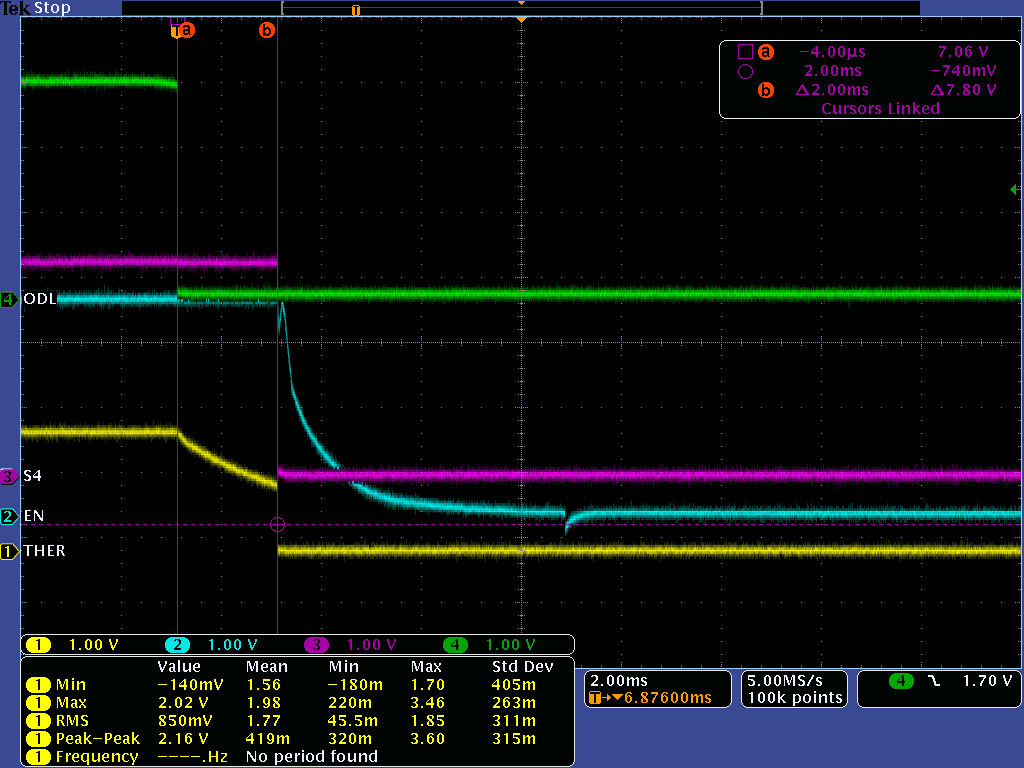

- Power rails (BUCK1~6 ) and RSMRSTB are off simultaneously.

- After system reboot, they read OFFONSRC register and found UVLO bit is set to '1'

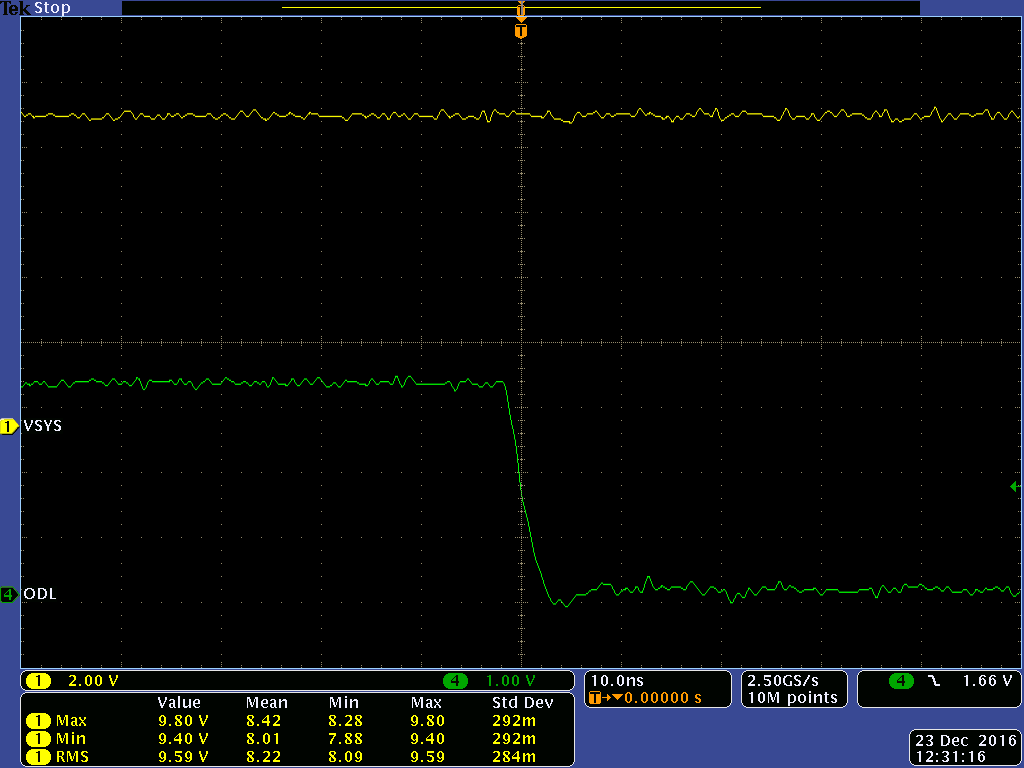

- They tried to measure VSYS at the moment system is turned off, but observe VSYS is stably around 7.xxV.

- SLP_S0/SLP_S3/SLP_S4 are beoming low around 2ms afterwards.

- PMICEN is turned off by their EC around 2ms after system turn-off as well.

Please let us know what we can check for further clarification.

Thanks!

Antony