Other Parts Discussed in Thread: CSD19536KTT, CSD

Hi,

I'm using the TPS2492 as a inrush-current limiter for a DC/DC converter that can be plugged into a supply.

Supply voltage (VIN) is 28 to 42 V.

Total capacitance to be charged is 4000 uF.

Maximum current drawn by the converter is 15 A.

The circuit works well to charge the capacitors at the beginning.

But when the DC/DC converter is enabled, the MOSFET will be turned off immediately.

I don't understand why the TPS2492 switches off the load.

The converter draws only about 1 A at startup.

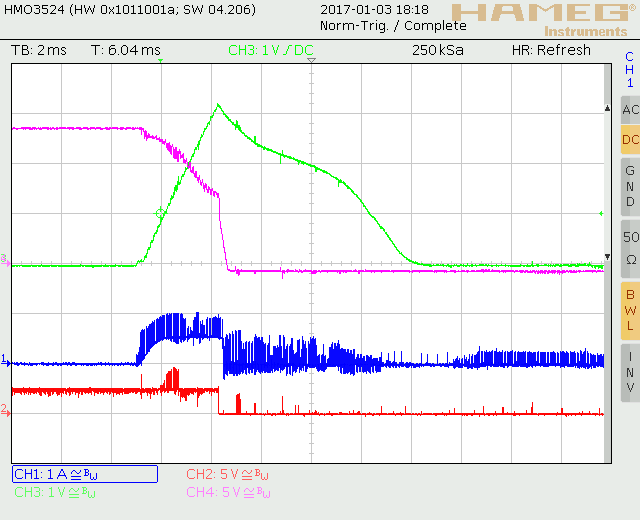

Here is a measurement:

CH1: input current (at VIN, measure with a current probe)

CH2: FLT_N signal (with pull-up resistor to 3.3 V)

CH3: timer capacitor voltage

CH4: MOSFET gate-source voltage

The VIN and VOUT voltage stays stable when the converter starts.

When I increase the timer capacitor from 3.3 nF to 10 nF, the voltage at this capacitor reaches only 1 V before the MOSFET is switched off.

How could it be that the MOSFET is switched off before the timer capacitor reaches 4 V?

Why will the gate-source voltage of the MOSFET be reduced when starting the converter?

With this low power there should be no power limitation of the MOSFET.

I've attached my excel-calculation.

Any suggestions how to get my system running?

Regards, Florian