Hello all,

I am using the Phase-Shift PWM Controller UCC2895 for a DC/DC full bridge converter of 10kW with a fixed frequency of 200 kHz.

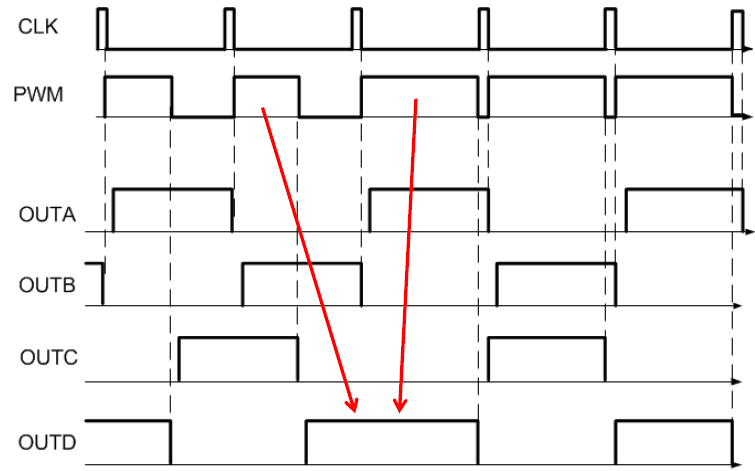

I am experiencing some problems with sudden changes of duty in the OUTC and OUTD not related with the comparison of EA and RAMP signals. The problem seems to increase or decrease depending on the working point of the converter (relation between Vin and Vout).

I have verified that the EA signal is completely stable and I have tried to add decoupling capacitors in the EA and the RAMP pins to ground but it did not make any effect. I also tried to change the RAMP shape to see if the problem was related with this signal (increasing R100) but it had no effect neither.

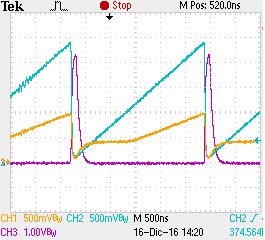

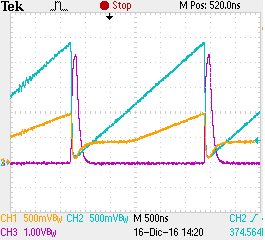

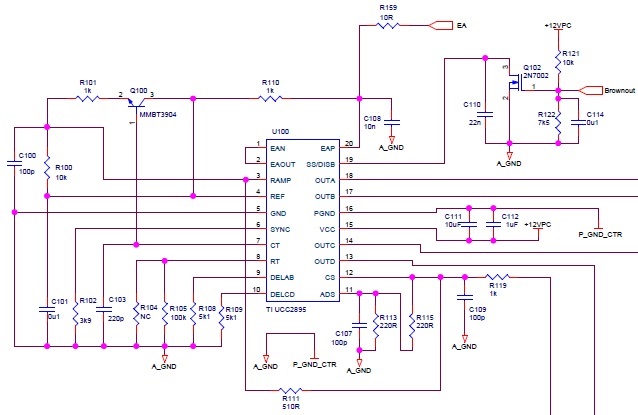

I attach the figures of the OUT signals and the RAMP signal. I also send you the electric scheme to show you the configuration of the IC. I can send you the gerbers too.

OUTA (amarillo), OUTB (azul), OUTC (rojo), OUTD (verde)

RAMP (amarillo), CT (azul), SYNC (rojo)

Configuración UCC2895

Thank you in advance.

Ramon