Hi team,

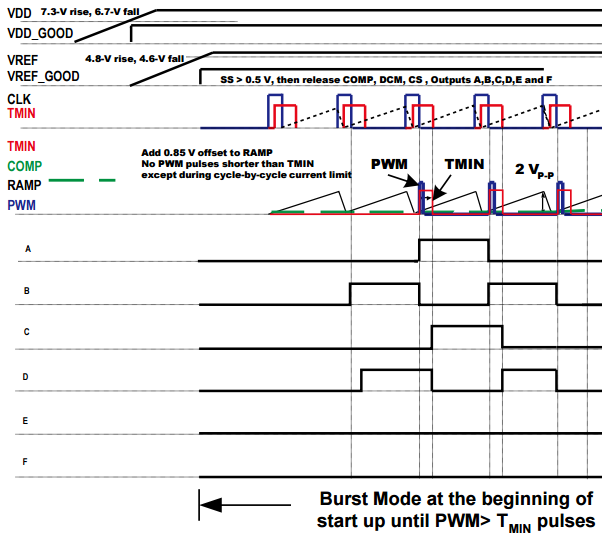

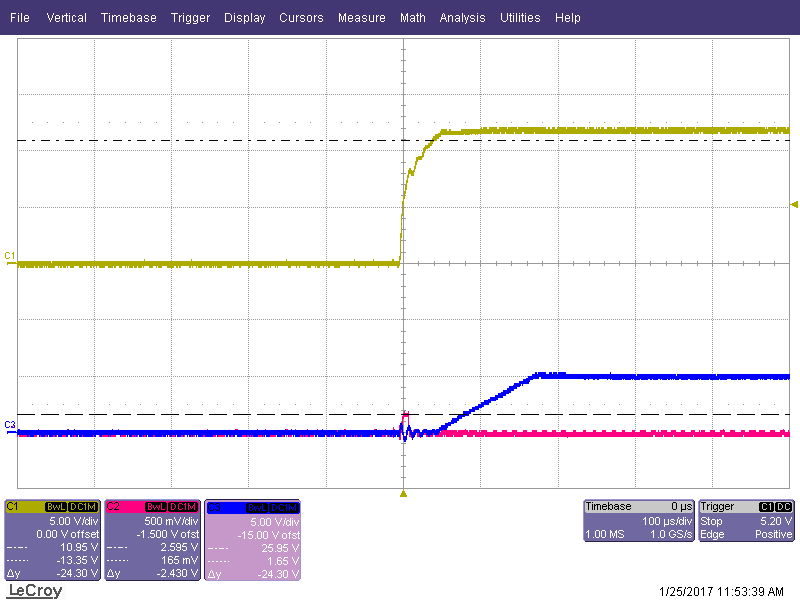

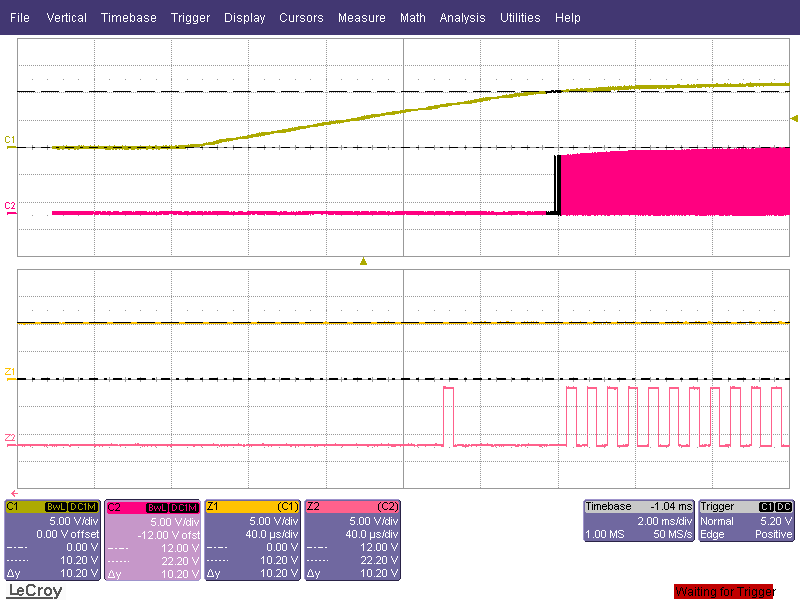

What is the duration time from VDD applied untill OUTx are fixed to low?

We presume those pins are high impedance for a certain period (eg, before VREF starts), is this assumption correct?

This is needed for designing.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.