Hello,

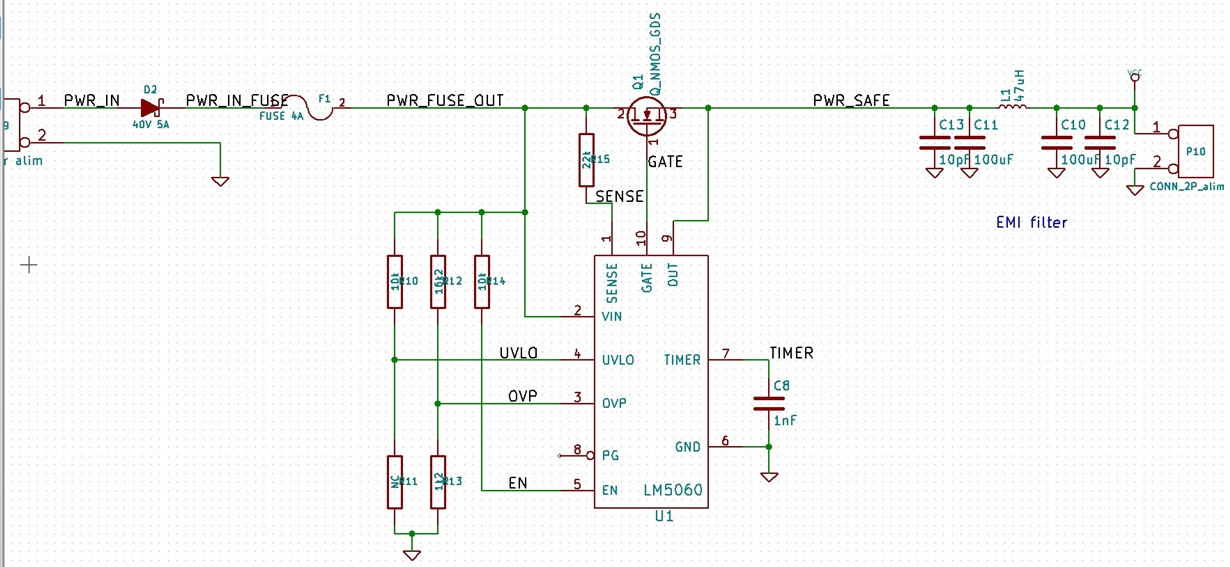

To protect our product from too high voltage power I have inserted a LM5060 before it.

I use the OVP and current limitation functions, the UVLO pin is connected to VIN as implied by the datasheet.

The OVP is set to 29V and limitation current is way higher than the 1A we need.

I've joint the schematic, Rds is 115mOhm

When I test it with a lab power supply, I start around 12V and gently ramp up to find the threshold.

It works perfectly and cut the power above 29V.

Now when I set the power supply to 35V or higher, and plug the cable, the LM5060 smokes, even with no load

We need a protection against 48V when our customers don't read the manual and plug our device to an active POE instead of 24V passive POE.

What is wrong with this schematic?