Other Parts Discussed in Thread: TPS7A47

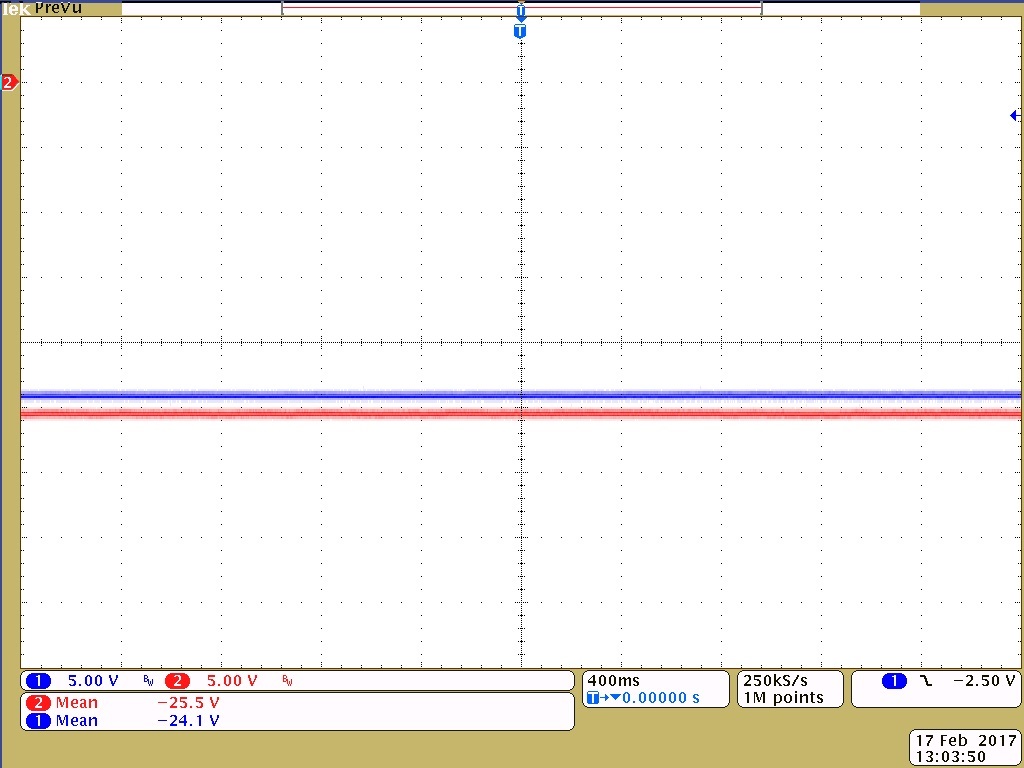

Using TPS7A family to provide regulated low-noise symmetrical (+/-24VDC) outputs per schematic fragment below:

TPS7A4701 and 3301 are set for +/-24VDC output (per data sheet), LDO input from Traco TVN 5-2425, trimmed up to +/-25Vdc. LDO input signal noise + ripple: < 2mVpp.

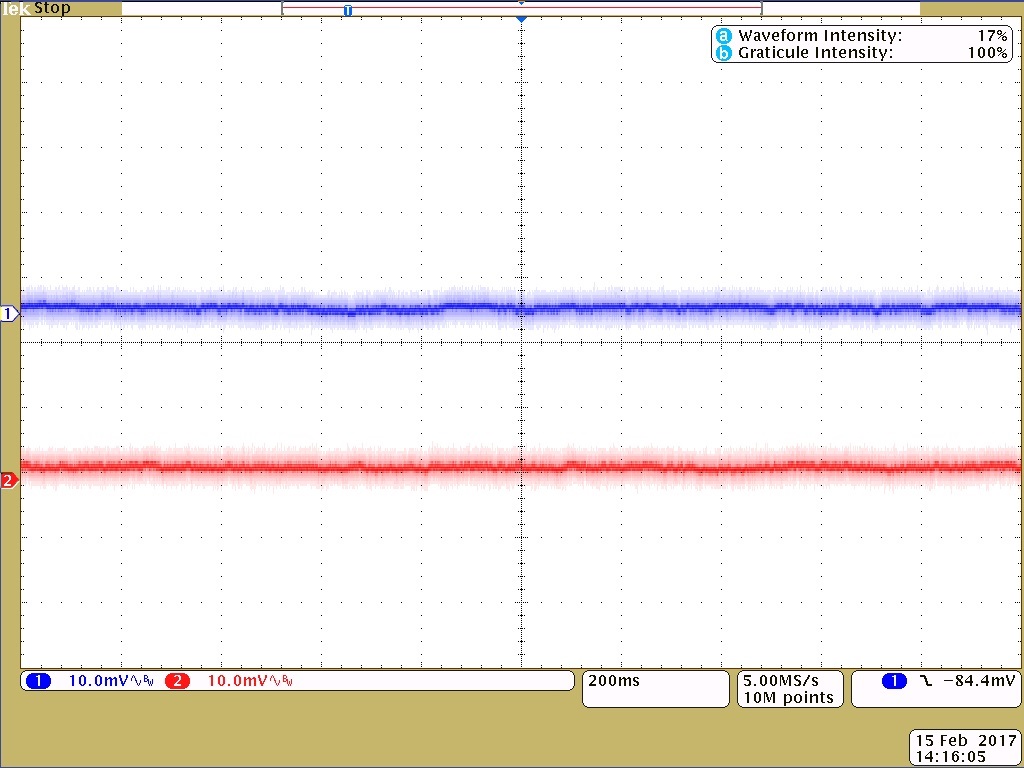

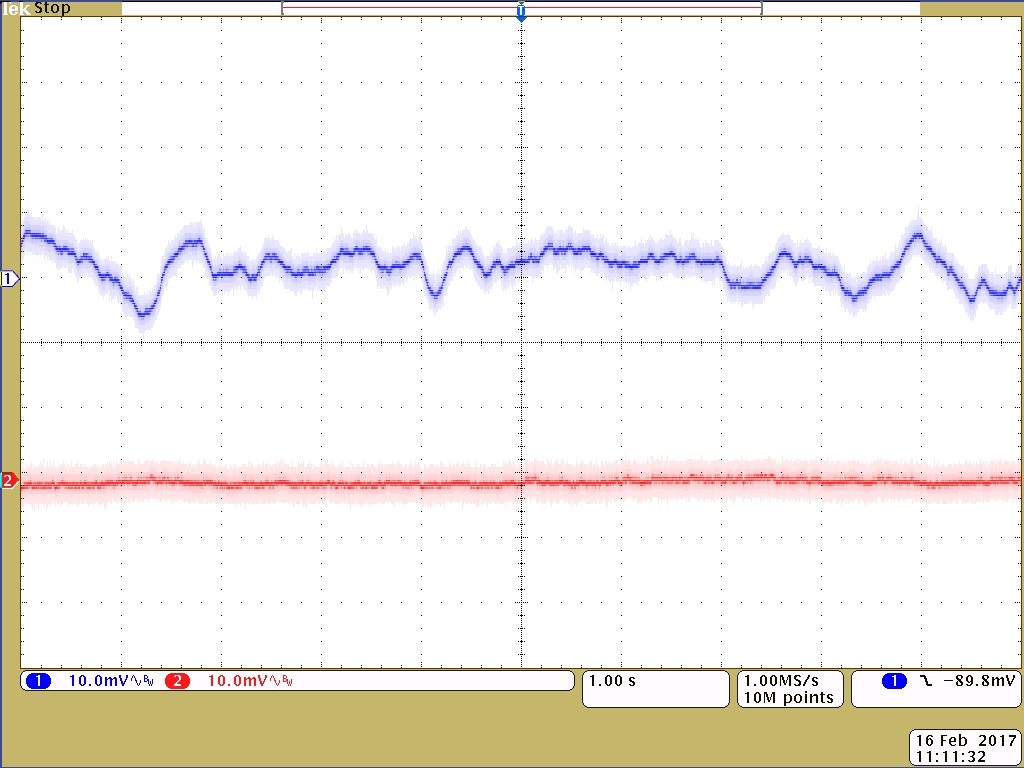

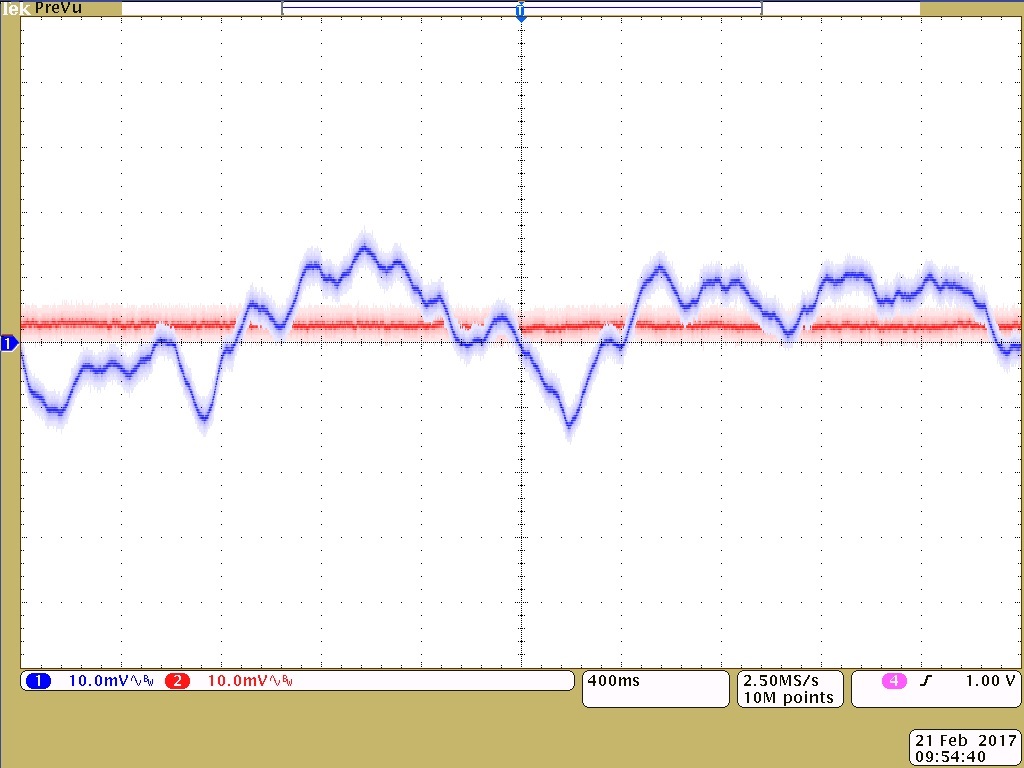

No load, open circuit scope measurements.

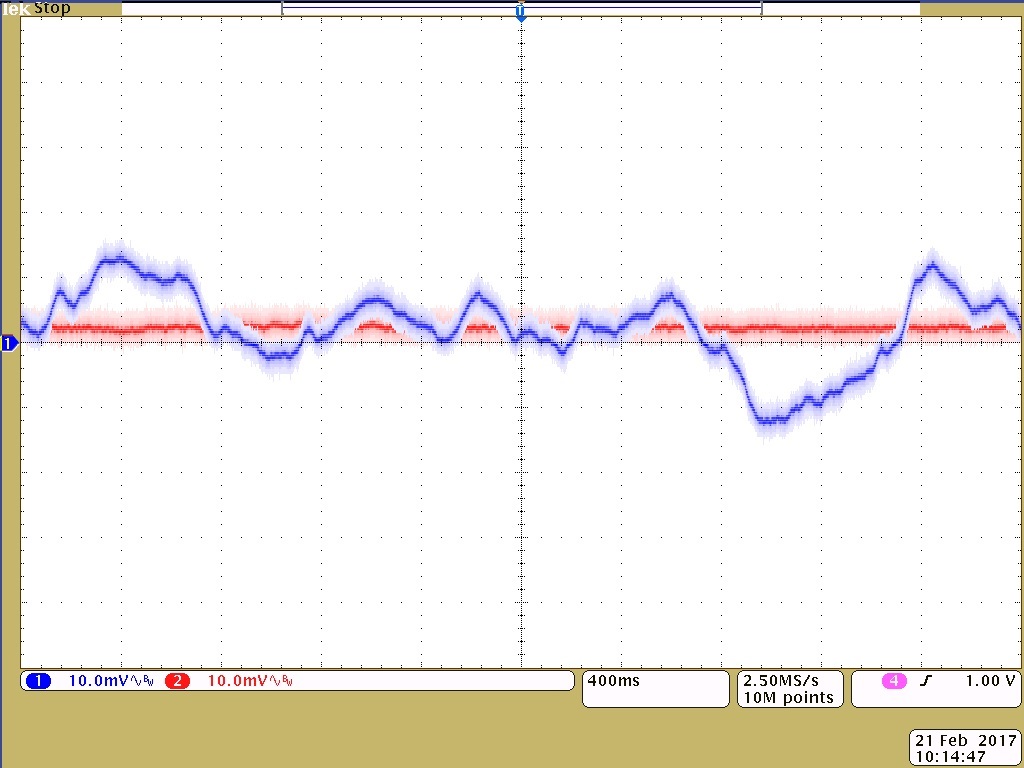

When PCB is powered up -> day #1 -> LDO signals measured @ J15/J16 pin 1: TOP trace - BLUE: -24VDC output, AC coupled., Bottom Trace: RED +24VDC output, AC coupled. Low noise on both rails.

PCB left running in LAB overnight: Noticeably higher noise on -24VDC LDO output. Power recycled. No change. Repeated on three (3) identical prototypes. Identical results.

PCB Layout shown below, top side assembly and Layer 1 routing. Ground plane on Layer 2.

Any help would be greatly appreciated.