Hello TI,

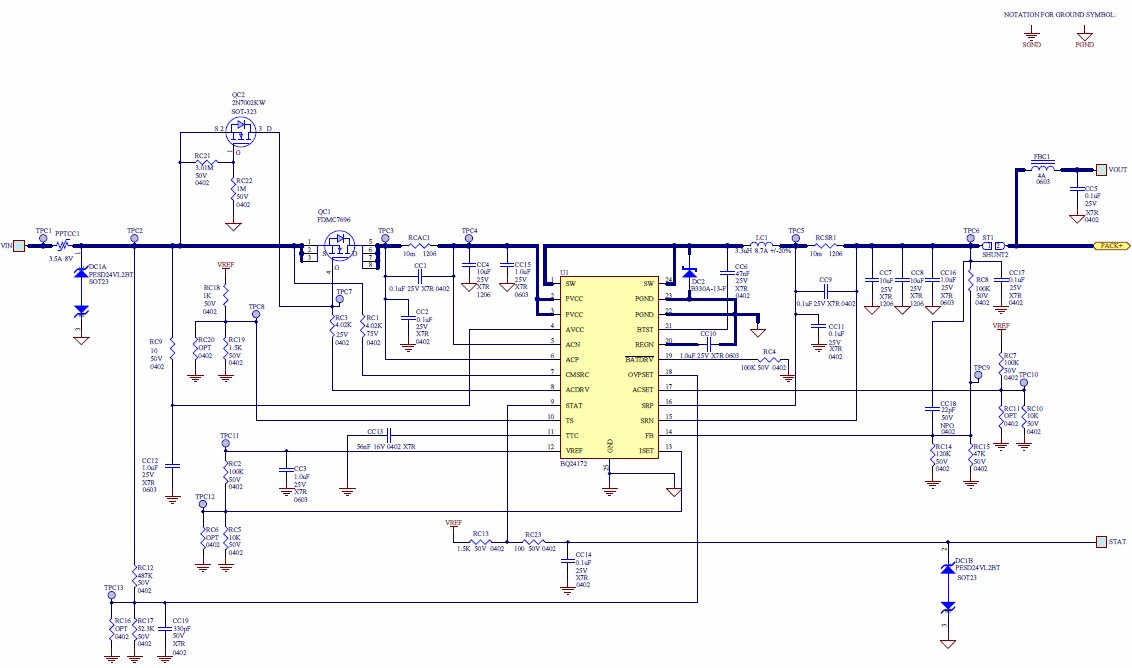

I've encountered an instability of PWM generated by the BQ24172 IC, specifically at pin SW (pin 1 & 24).

This issue happens when in CC mode and in steady-state where the battery simulator is fixed at 7.0V with 1.5A max. The charge current is 1.35A max..

The pattern of my PWM is that it generates 2 duty cycle: 40% and 87% with Vin=12V and F=1.67MHz.

What is the possible root cause of this PWM instability at steady state?

Thanks in advanced.