Dear All,

we are using BQ76200 in our design and We have a problem with high si de driver BQ76200 in high switching frequency (more than 100Hz)

de driver BQ76200 in high switching frequency (more than 100Hz)

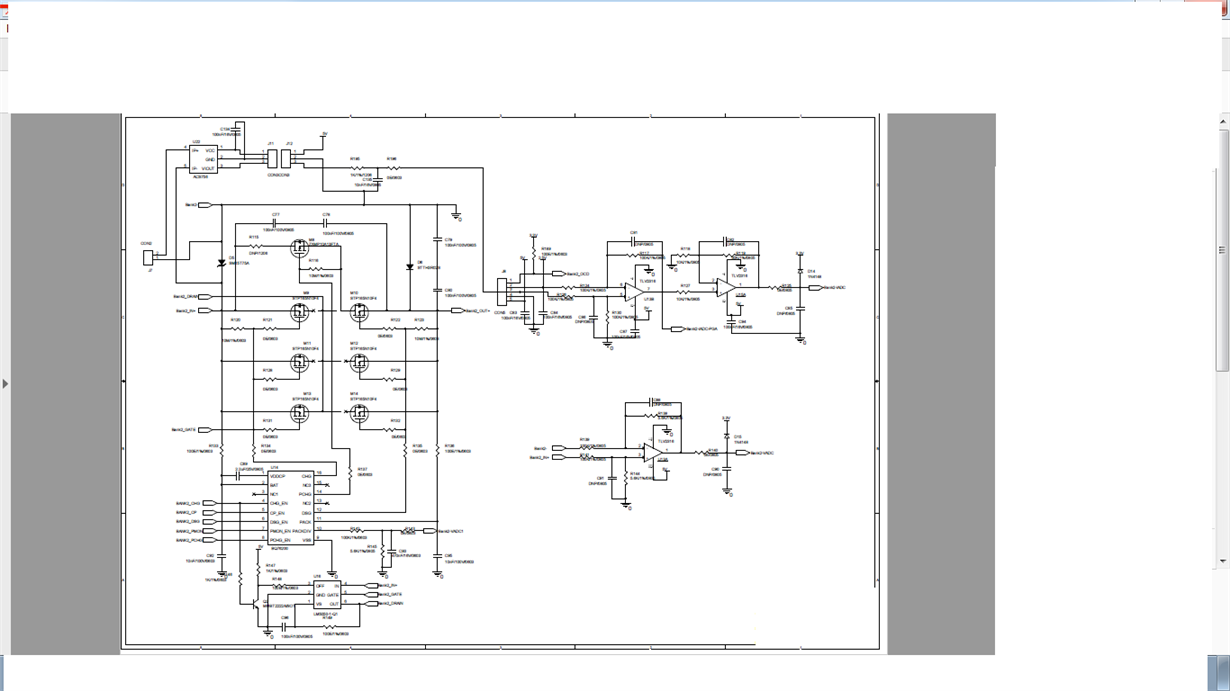

I have attached schematics of BQ76200. Kindly review and give solution.

Non Populated Components:

R146,R147, R148,R149,C96,Q2,U16

M13,M14,R115,R116,M8

Value Changes:

C89 = 2.2uF (2 in parallel)

NOTE: All the MOSFET Drain Connected electrically through a Heat Sink.

Rgds,

Aravind.