Hi,

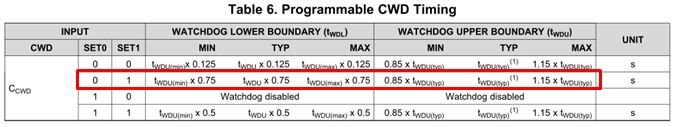

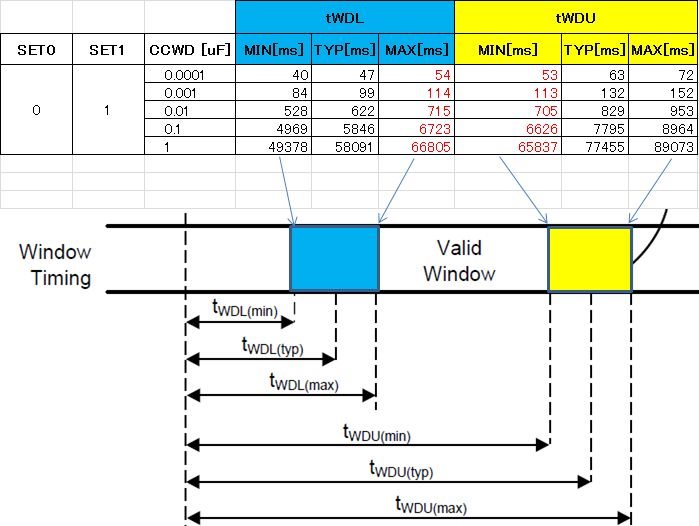

Now I'm calculating tWDL and tWDU at SET0 and SET1, then the tWDL(max) may be higher than tWDU(min) as attached. I think this means there is no valid window at considering WDI timing from MCU. Can you confirm it and give your comment?

Best Regards,

Satoshi / Japan Disty