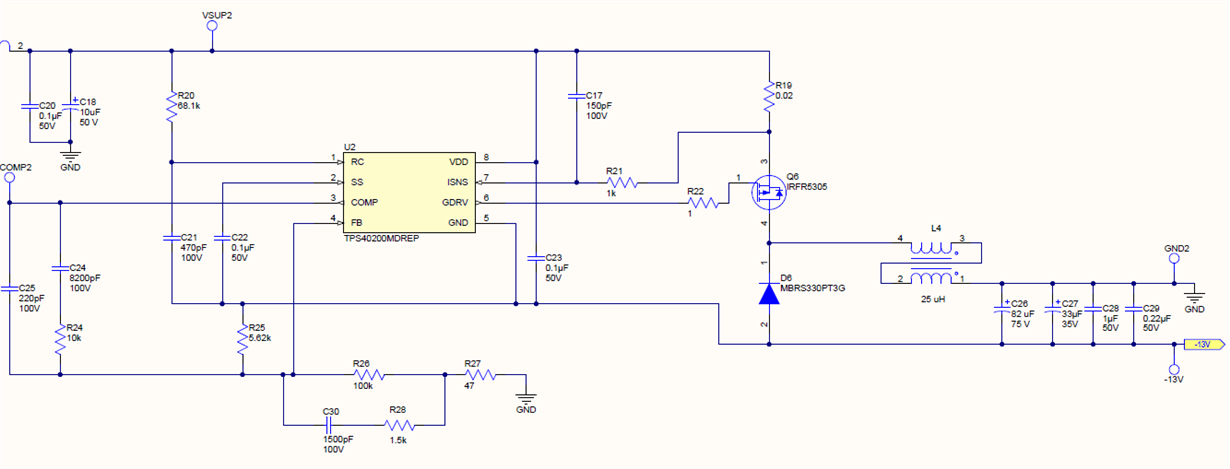

The design in question is an inverting -13V supply from 28-36V input (VDD="VSUP2"). The exact same design/layout/values/etc works fine in non-inverting +13V form, but when the inverting switcher turns on (begins switching), the TPS40200 IC begins drawing approx. 0.013 A @ 20 Vin.

NOTE: 1) C18 and C20 actually connected from VDD to -13V output. 2) Inductor L4 value is actually 100 uH

TWO QUESTIONS:

1) What do you think might be causing the IC to draw excess current?

2) Also, the only way I can get the supply to start (overcome OC conditions, upon startup) is to briefly jumper TPS40200 pins 7,8. After startup, the jumper can be removed and the circuit continues to operate. Do I need to increase the values of R21 and C17 in the ISNS network?