I have used the bq25890 in my board.

When the battery voltage is above 3.5V, everything works normally.

But when the battery voltage is bellow, it works abnormally.

I use 2 boards each with its own battery for test: Board A with Battery A, Board B with Battery B.

The 2 batteries are both depleted.

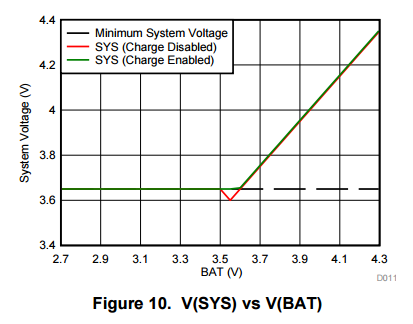

The SYS_MIN regesiter is not configured, so the SYS_MIN is the default value: 3.5V.

1. Board A with Battery A

VCC_Bat is 3.0V and the VCC_SYS is also 3.0V.

2. Board B with Battery B

VCC_Bat is 2.8V and the VCC_SYS is also 2.8V.

They are both not above 3.5V!

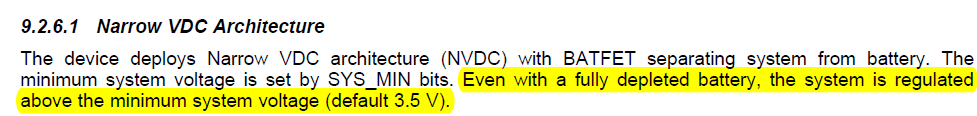

According to the datasheet:

The Sys Output of bq25890 should always above the SYS_MIN (defalult 3.5V).

What's wrong with that?

I have a BUCK DCDC to convert SYS_VCC to 3.3V after bq25890, since the voltage is below 3.3V, the whole system cannot work!

Please help!

Frank