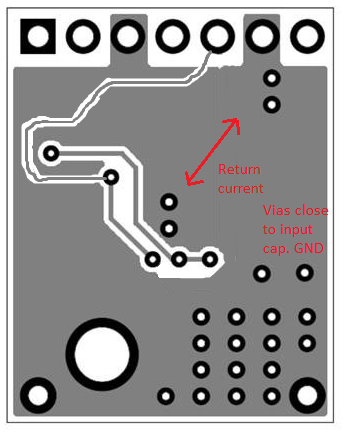

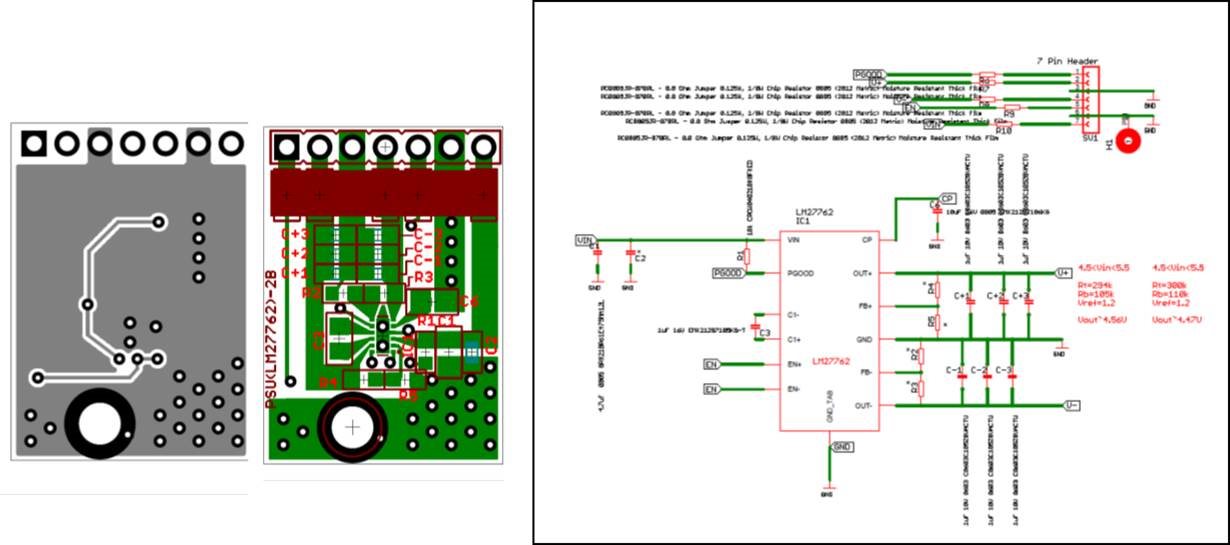

I have been having similar issues to this post (e2e.ti.com/.../582389 ). My question is that I have connected the GND pin to the thermal pad, which is obviously a very close trace. The attached diagram shows that the thermal pad has two vias to the ground plane on the bottom layer. My question is - even though my trace from the ground pin out to the Cout capacitor is long and narrow, shouldn't the thermal pad via's do the trick for avoiding this inductance issue? If so, what else could cause startup issues for this chip?

My design allows either a ~4.8V USB source or a 5VDC source form a voltage regulator. The USB connection starts up without issue, yet the 5V source always starts up in a fault state with the negative output being much too low and the circuit ringing. If I start up with the USB source and then transfer to the 5VDC source without power interruption the circuit runs fine. As well, I can short the negative output momentarily and then the circuit will run fine once I remove the short.