I have questions about UCC28251.

Question 1 :

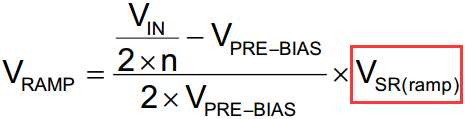

This question is about dataseet p.32 formula(22).

Vramp={Vin/(2 x n)-Vpre-bias} / (2 x Vpre-bias ) x Vsr(ramp)

Please tell me the optimum voltage of Vpre-bias under the following conditions.

Vin=180~210

Vout=125

Iout=1.6A

Question 2.

We try to use the external clock.

- Please tell me the relationship between registor of RT pin and external clock.

- Please tell me the peripheral circuit that applys to RT pin.

- Please tell me the timing of applying the external clock.

- Please tell me the notes when the IC starts to enable.

Best regards,