Other Parts Discussed in Thread: BQEVSW

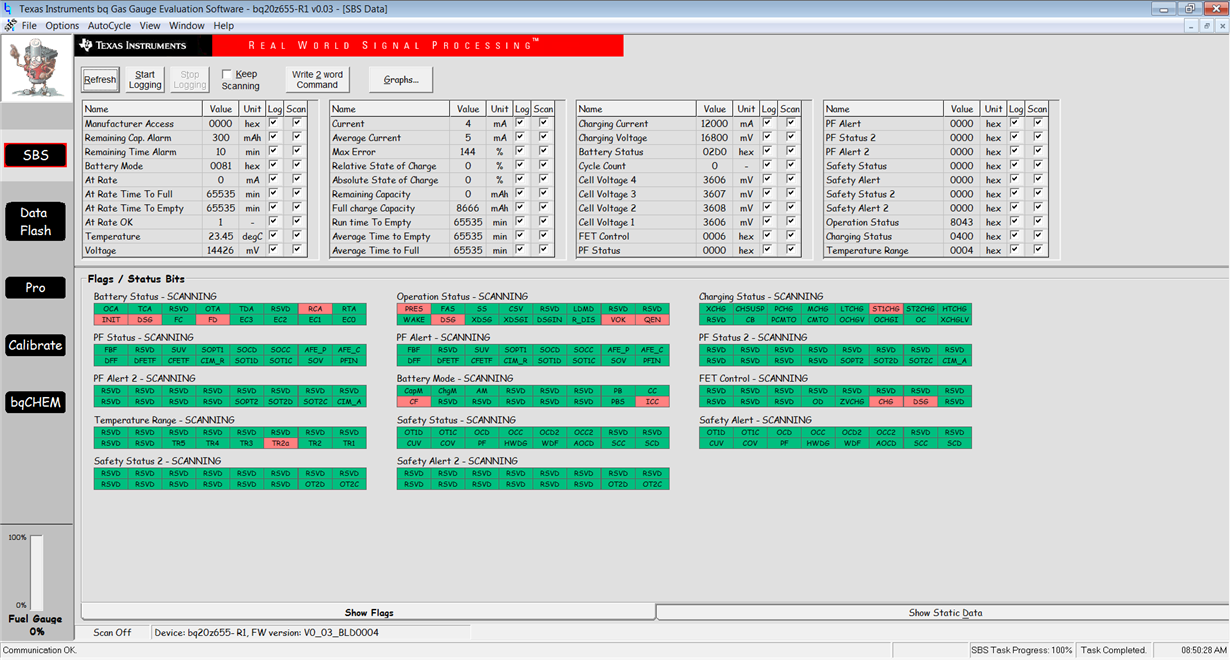

I cannot get my unit to sleep. I'm not seeing either the CHG or DSG FETs turn off.

I have a non-removable battery so [NR] = 1 in CfgB. I have set my sleep current higher than I need (50mA) for testing purposes. When "idle" I'm seeing about ~3mA of absolute current. I don't understand why it won't sleep.

The 'PRES' pin on my design is grounded. But I have read that "If the [NR] bit is set, the PRES input can be left floating, as it is not monitored." So I'm am interpreting that this is not the issue, correct?

Also, sending an 0x11 in the manufacturer access line does not send it it sleep either.

I have attached my .GG file.032817_3.zip