Hello,

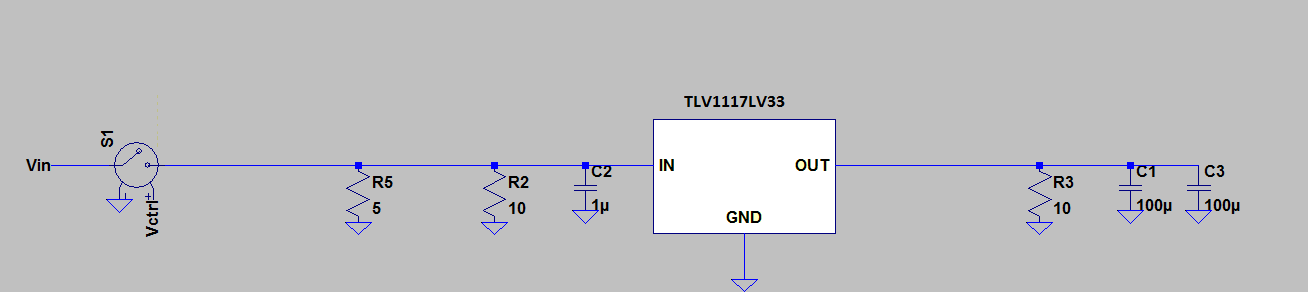

We are having some issues with the TLV1117LV33 in one of our products. The LDO has a nominal input of 5V, generated by a buck converter. The output is used to power a PLC chipset (microcontroller + AFE).

A few units have been returned with bad 3.3V rails. The measured rail voltage was only about 1.5V instead of 3.3V. After disconnecting the LDO from the load (there is a 0ohm resistor on board), the LDO output increases to about 4.4V. Replacing the LDO fixed the problem on the devices. We did not find any other failed components on the 3.3V rail or 5V rail. There is no visible sign of damage on any of the parts or the board.

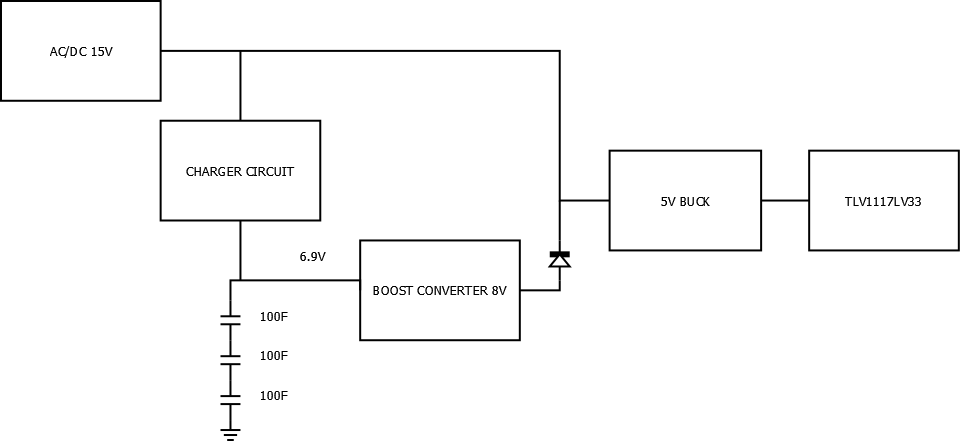

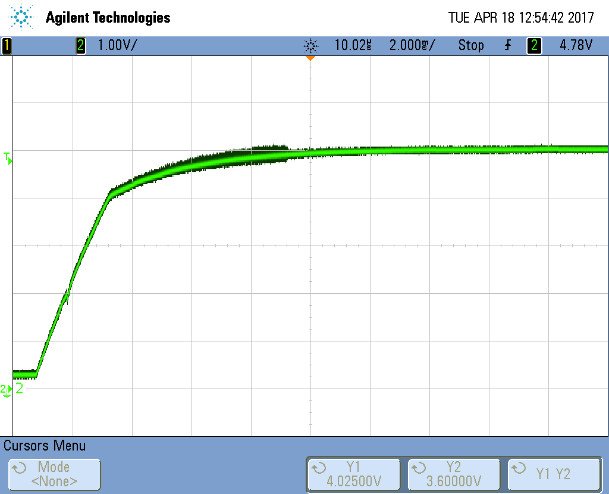

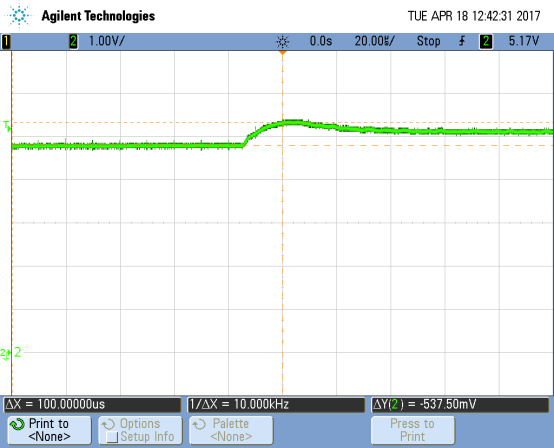

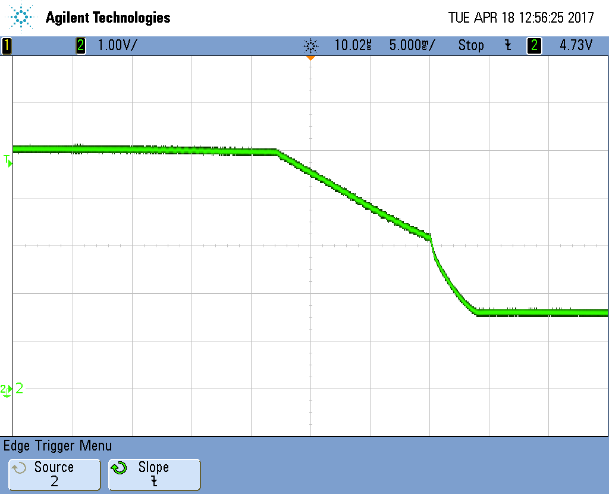

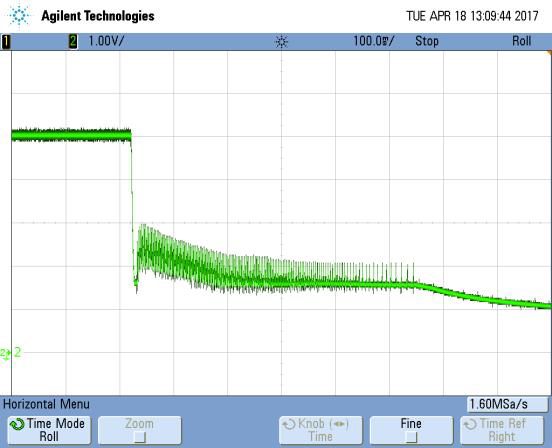

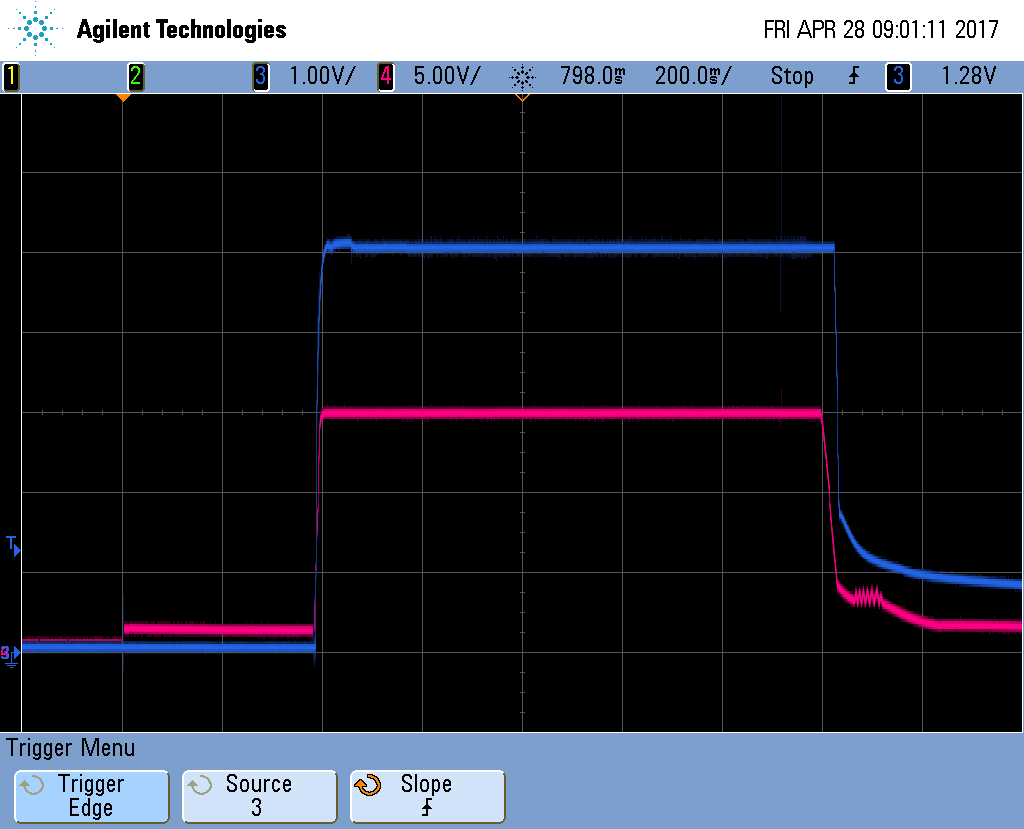

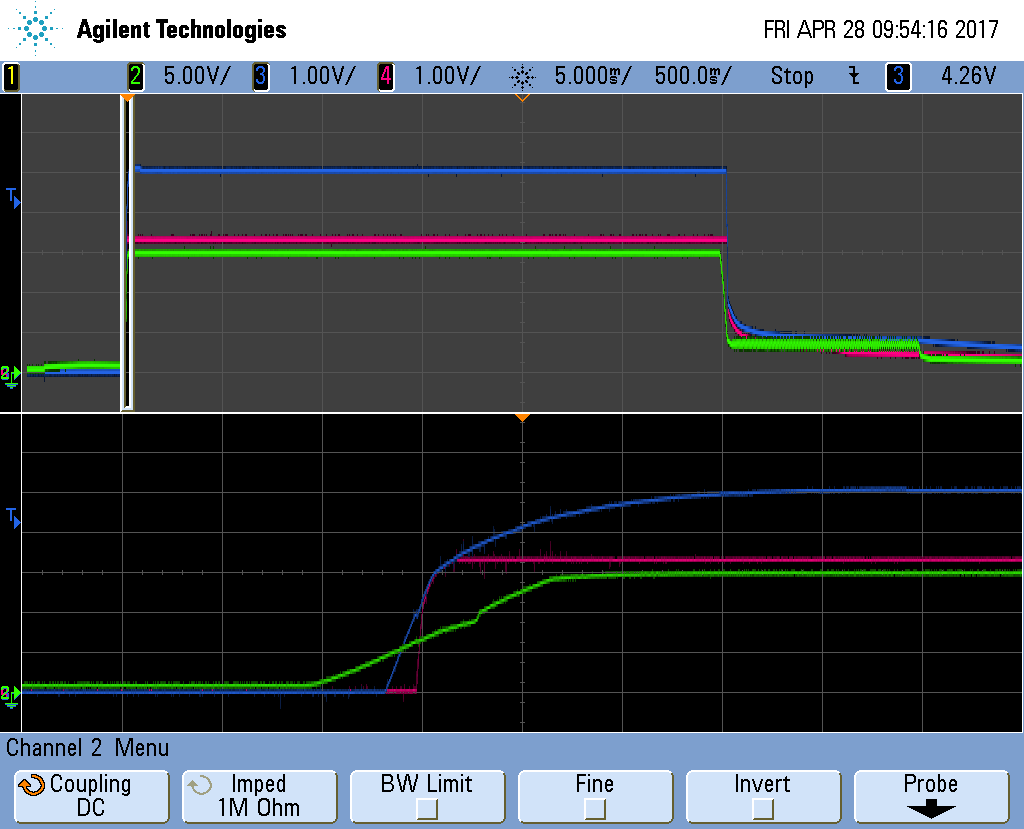

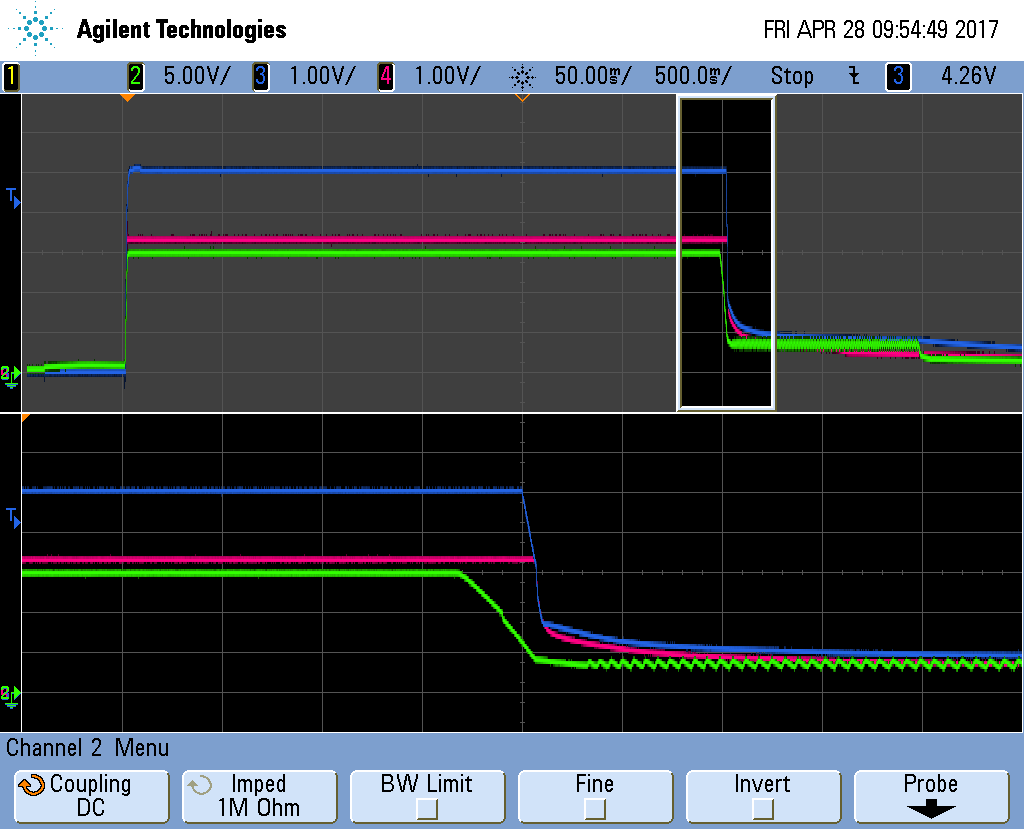

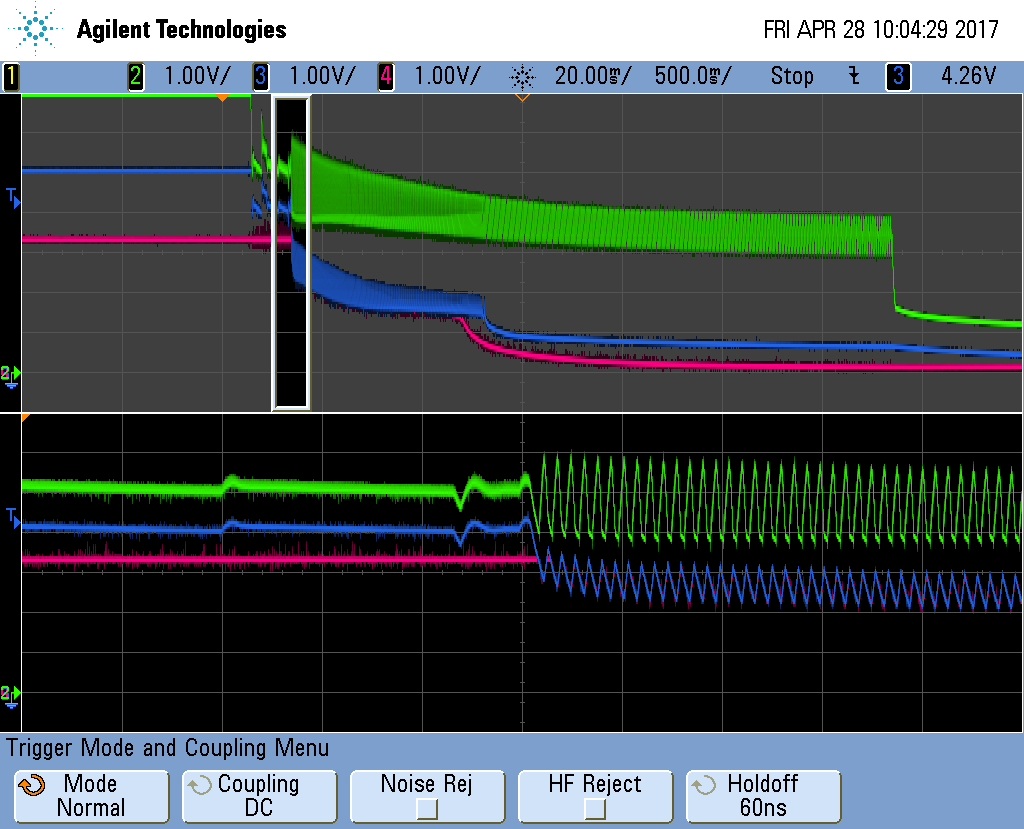

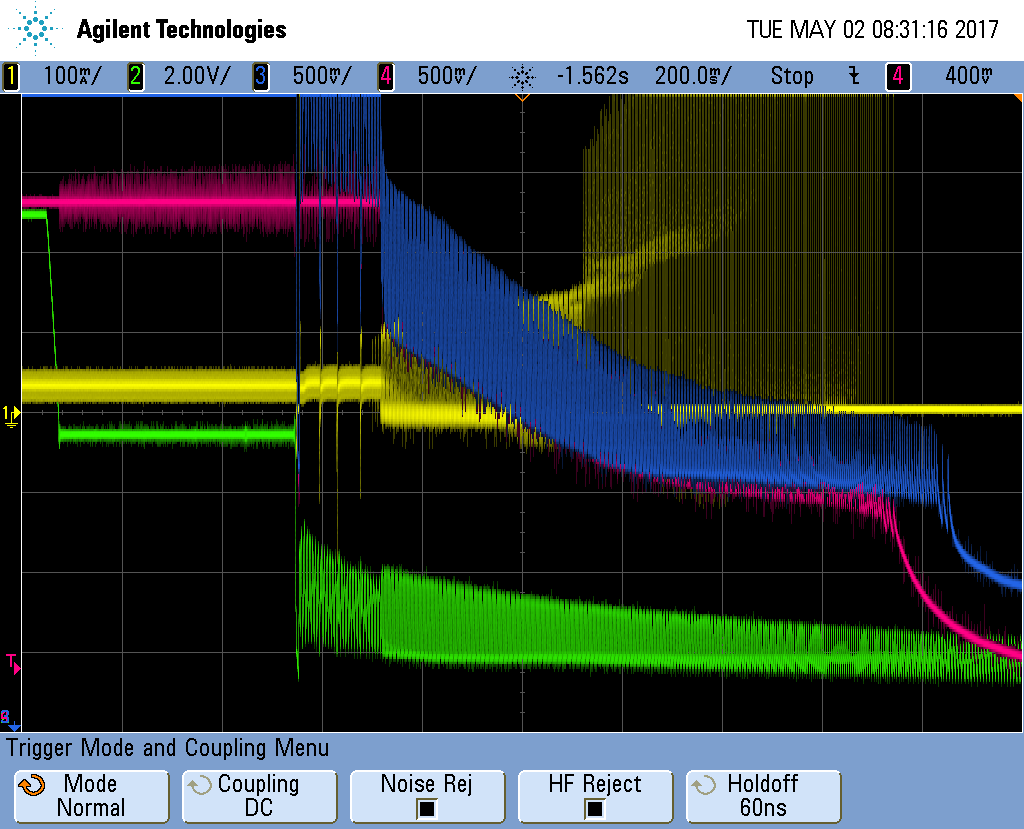

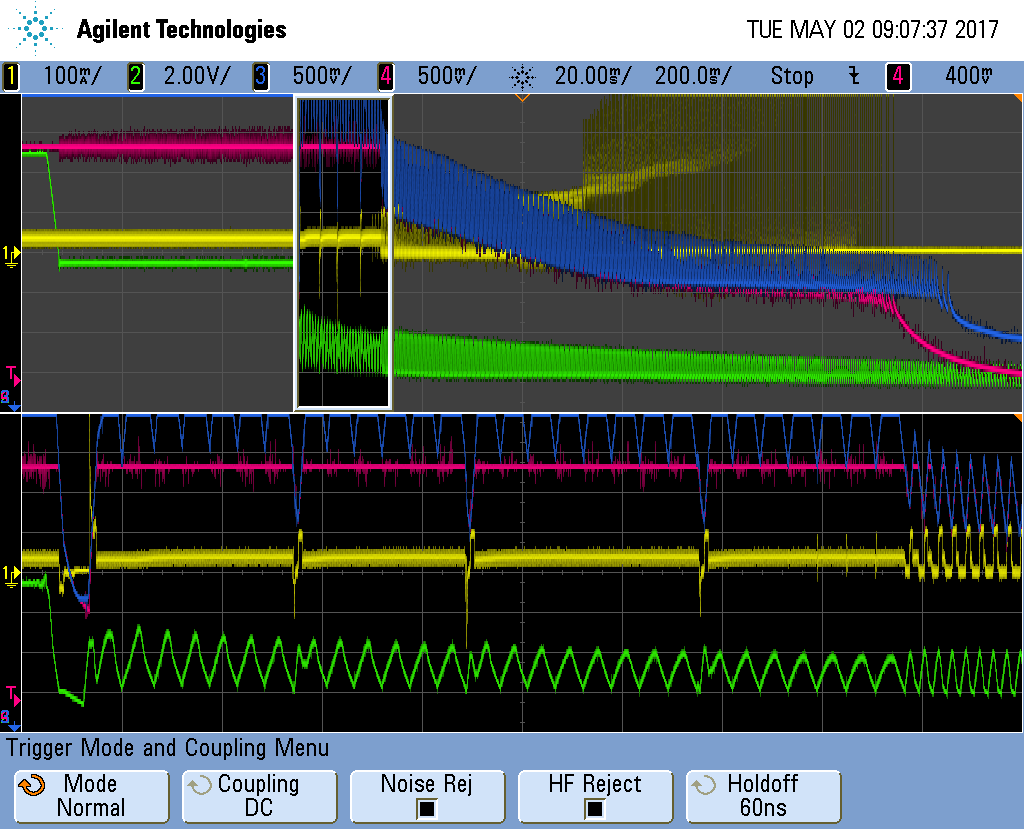

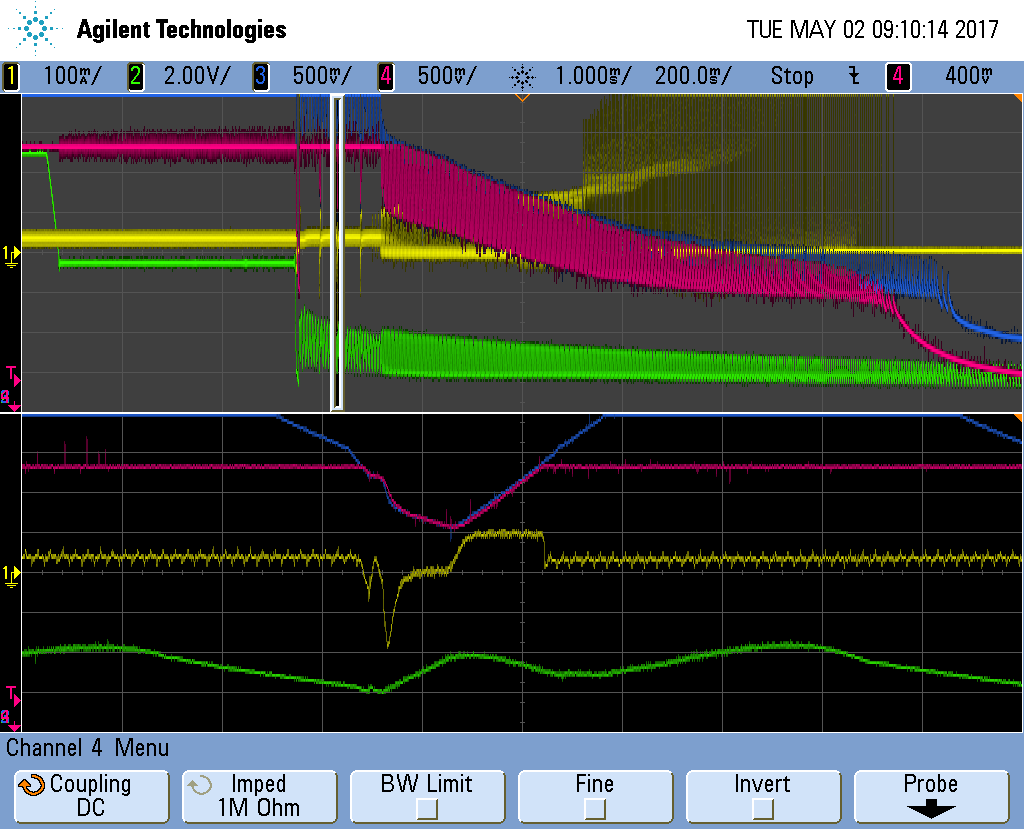

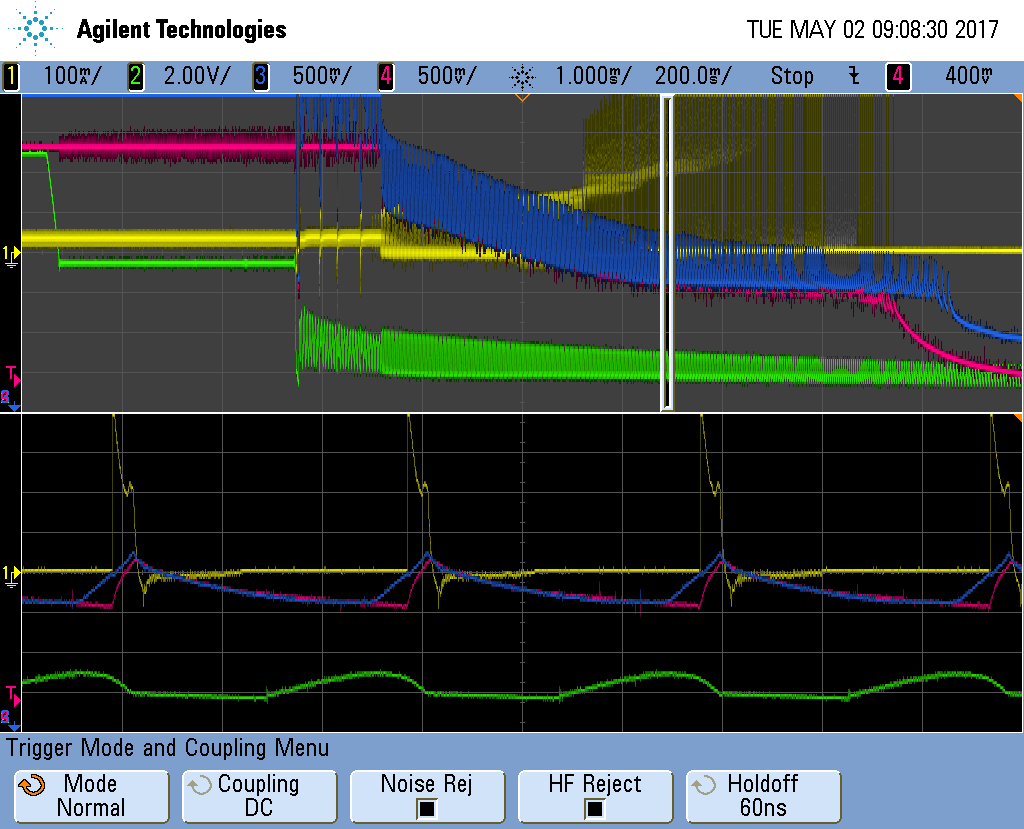

We did several tests to try and determine the cause of the failed LDO's, but have not found the root cause. So far, overvoltage seems to be the only reasonable explanation, although we would expect other components on the 5V rail to fail much sooner than the LDO. We also did some tests with the 5V buck converter and found it very hard to generate any significant overshoot (startup, load transient, input transient, ...). We do have another theory that oscillation may be an issue. The devices have backup power (super caps) which is generated by a boost converter, which in turn powers the 5V buck. A sudden change in load at the end of the 'last gasp' can result in the rail voltage oscillating slightly. Meaning it suddenly jumps back up due to the load dissapearing. Though this also does not cause any significant overshoot.

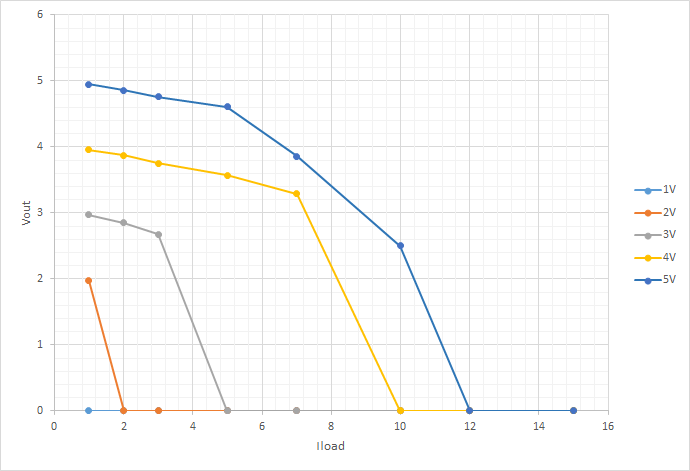

We also did a controlled overvoltage test on the LDO to see at what point it tends to fail and found that the 6V rating in the datasheet is very conservative, so it seems unlikely that a small amount of overshoot would damage the device permanently.

As for other possible cause, the device has overcurrent and overtemperature protection so those seem unlikely. Furthermore, the 3V3 rail is normally never loaded excessively.

The LDO has a 2.2uF input cap and a 10uF output cap.

Questions:

- What would typically cause this type of failure mode (LDO voltage too low under load, too high without load)?

- Can 'oscillation' or a varying input voltage cause damage to the device (seems unlikely)?

- I've heard it's possible to do failure analysis at TI.

- Do you think this would be appropriate in this case?

- What would be the approximate cost for us?

- How long does failure analysis typically take?

Kind regards,

Sam