Hey,

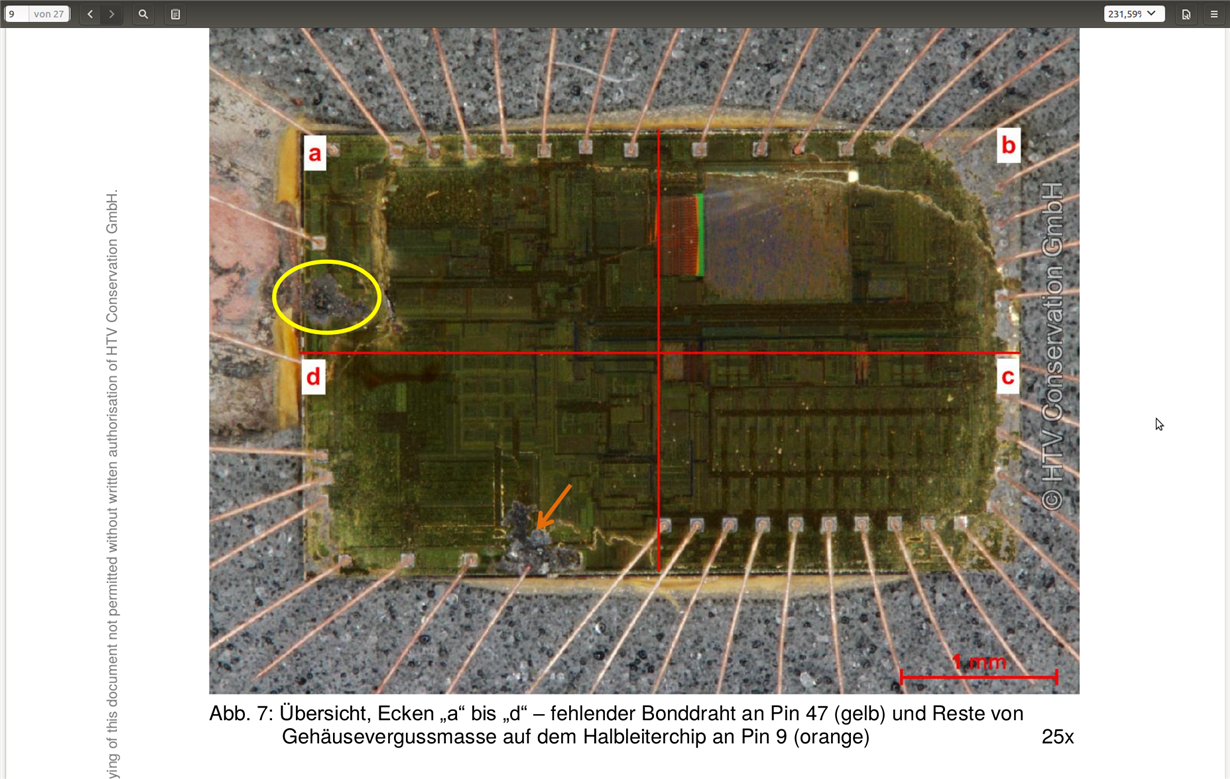

we are using the bq77pl900 with 10 series cells and are experiencing some defects of this chip. The PACK and BAT pin of the chip breaks. There must be some overcurrent flowing into these pins. We chemically opended one broken chip and you can see that defect there. See below.

Right now it's unclear why that overcurrent flows into the chip. I suspect that the "step down charge pump" could have some defect and draws too much current. I did the following tests and checks:

- The three capacitors for the charge pump are ok

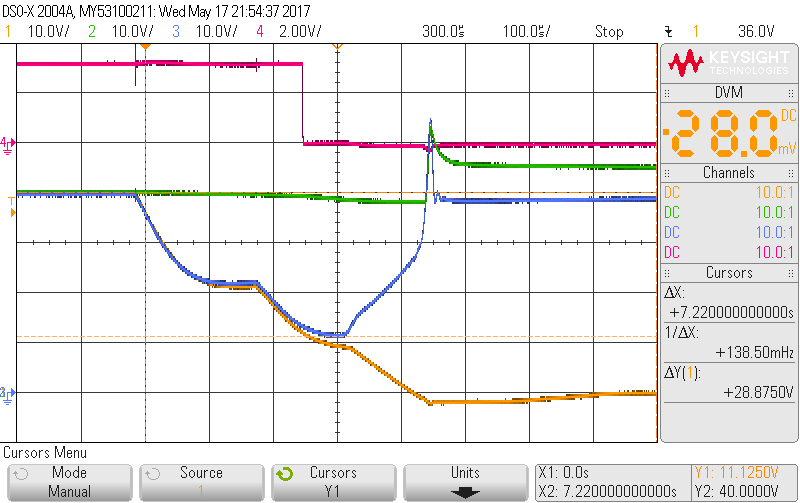

- Tested max load for 5V power supply with constant current of 50mA and ambient temperature of 100°C for several hours.

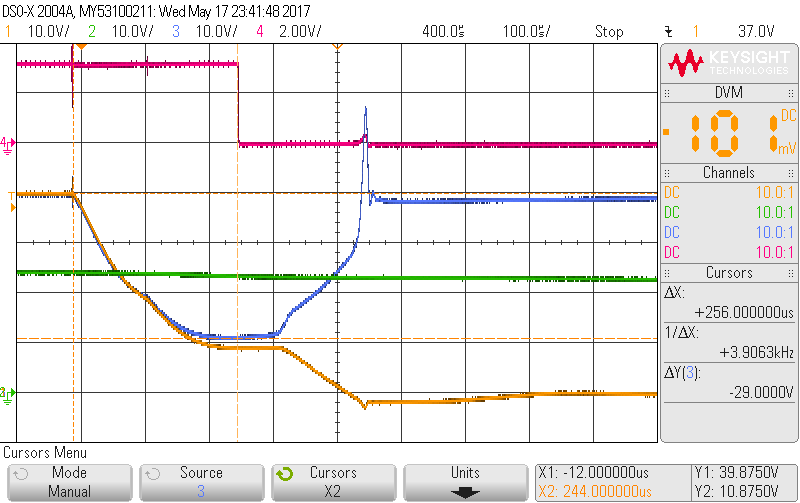

- Tested max load for 5V power supply with constant current of 50mA and additionally over currents of 100mA for 7,5us with 20kHz. -> Chip temperature rose to 90°C@25°C ambient but chip did not break.

What else could be the cause for the BAT and PACK pin to break?

Ich can give more information if you need.

Thanks very much,

Anton