HI,

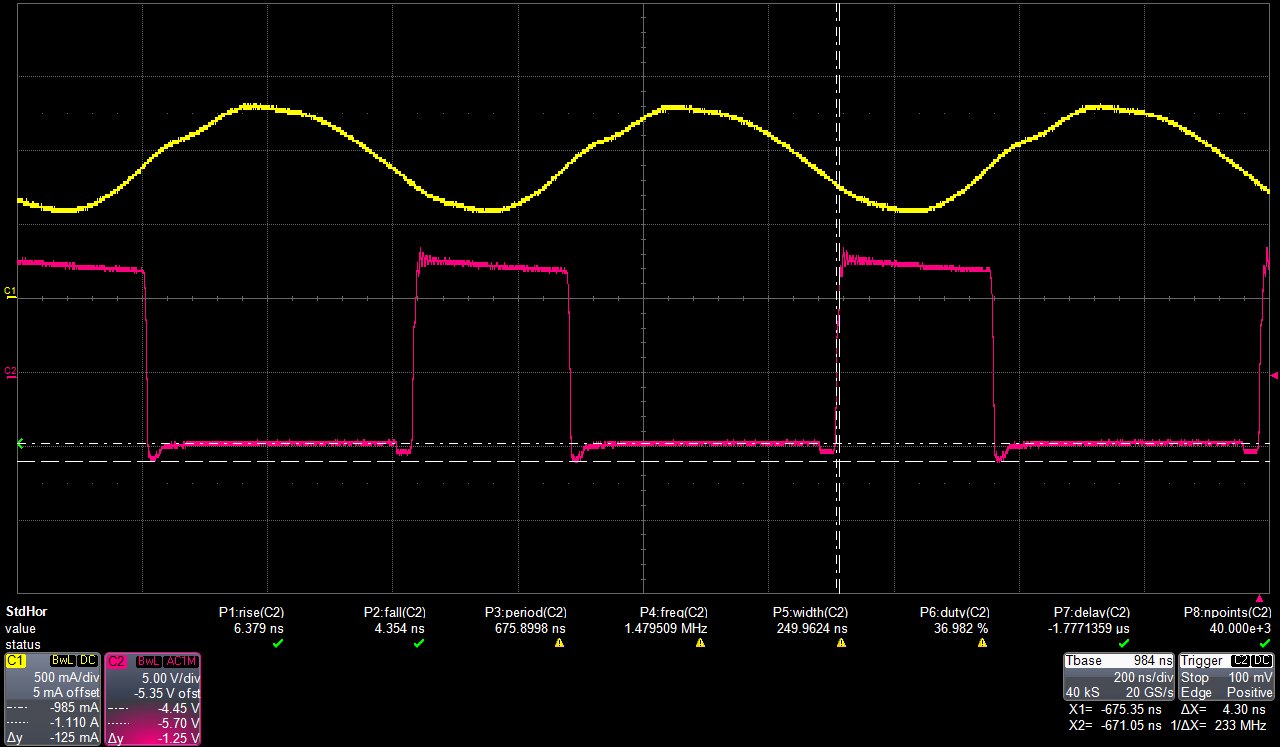

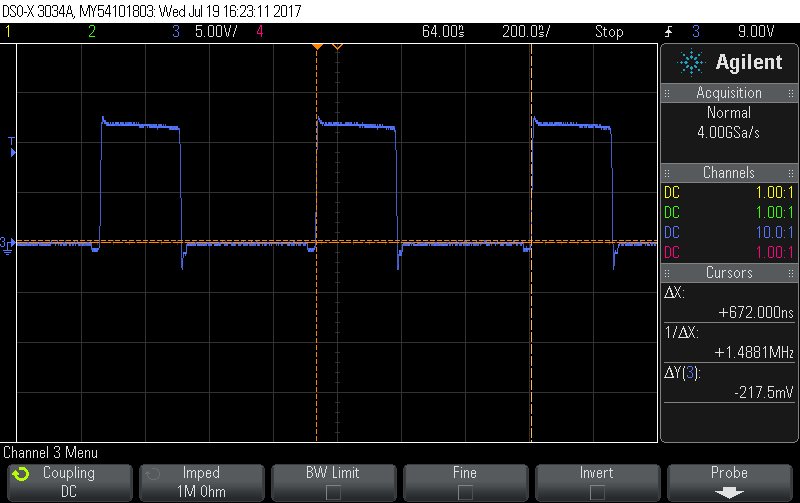

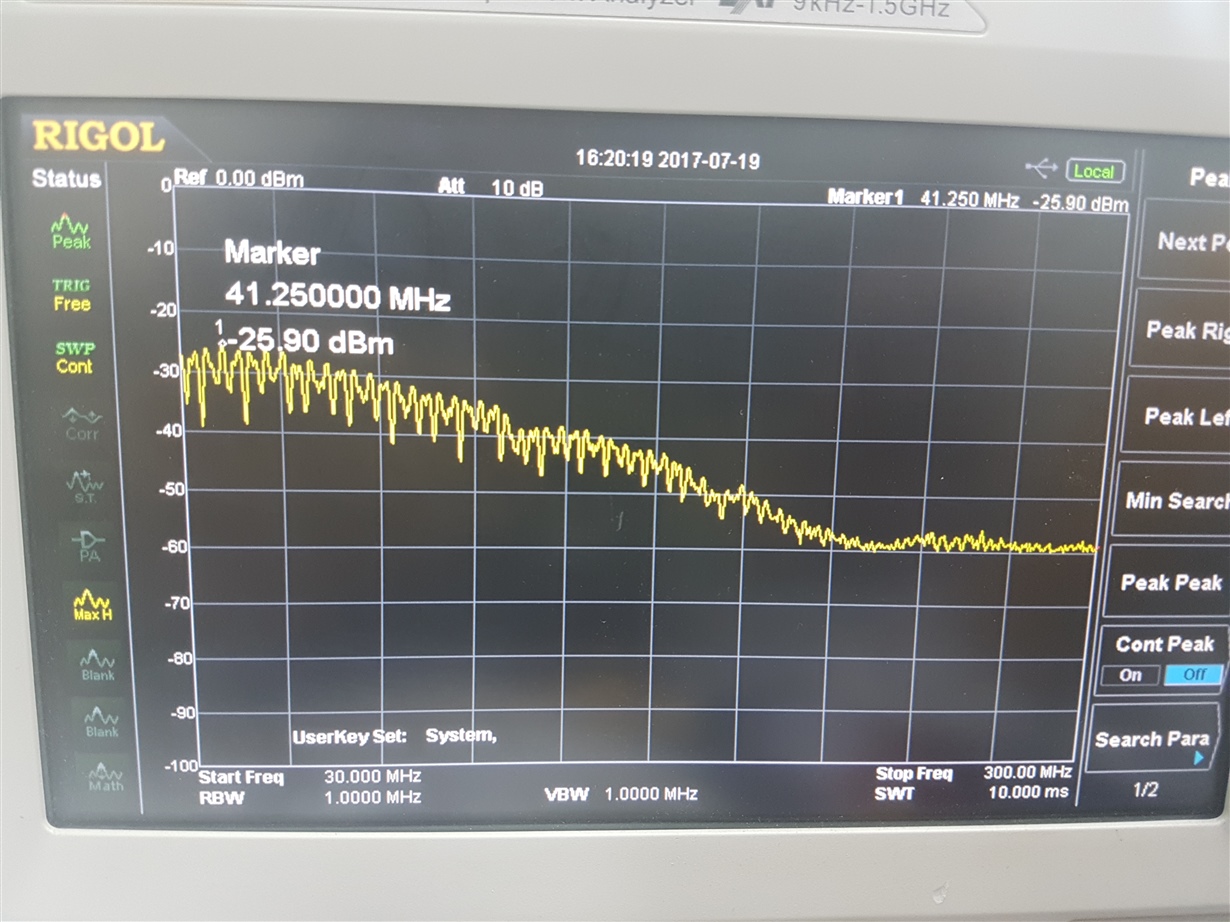

I'm using the bq25890 in my design to charger a 7200mAh battery. In charge mode, my device is failing radiated emission test, and the source of the emission ihas been narrowedd down to the charger IC. Unfortunately this IC does not give enough flexibility to play with the settings (like gate driver slew rate control, etc)

- Are there equivalent IC's that have better EMI response that TI carries

- Are there any suggestions to help reduce the noise level

I'm charging at a rate of 3.5A using a quick charger IC that provides a 11.5V @ 1.5A.

The device is charging through USB via a wall wart charger (quick charge)

Thanks