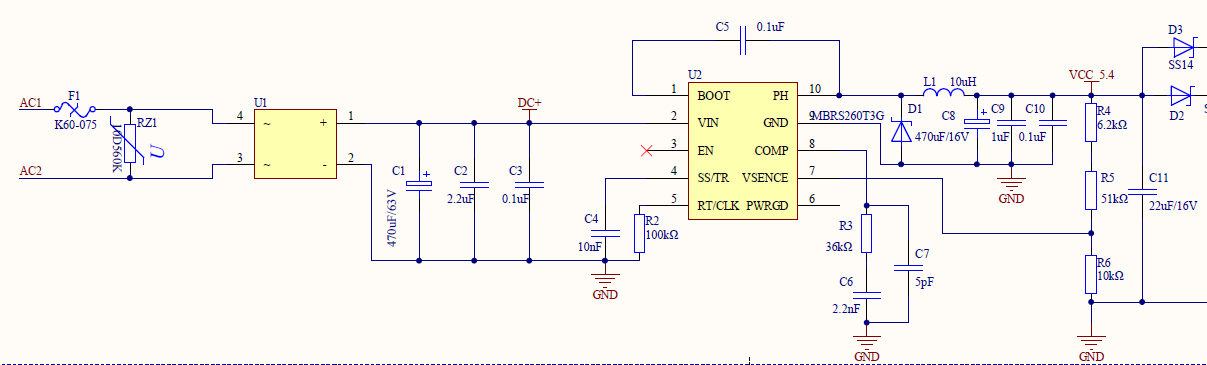

I used TPS54160 design a power supply, input voltage AC12-24V, rectifier filter DC voltage of about 40V (consider the grid voltage fluctuations + 20%), the output voltage of 5.4V, the output current of 0.1-0.3A.

Question 1: The chip of PIN3 with enable and undervoltage lockout function, because the output power range is wide, the divider resistor is not good, in order to simplify the circuit, so the pin is floating, Is this application risky?

Question 2: TPS54160 Switching frequency adjustment to 1.1MHz, inductance L1 election 10uH (power inductor MS127-100MT 5.4A (Isat) -0.0216Ω), filter capacitor selection 470uF electrolytic capacitor and 22uF ceramic capacitors. The Chip PIN4 and PIN8 of the parameters of this election appropriate? Such as the below SCH R3, C7, C6, C4, R2.

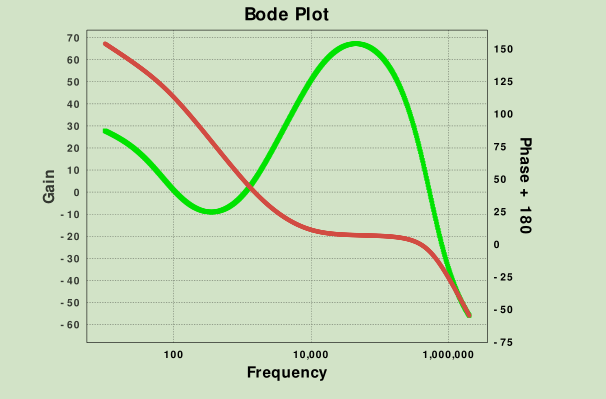

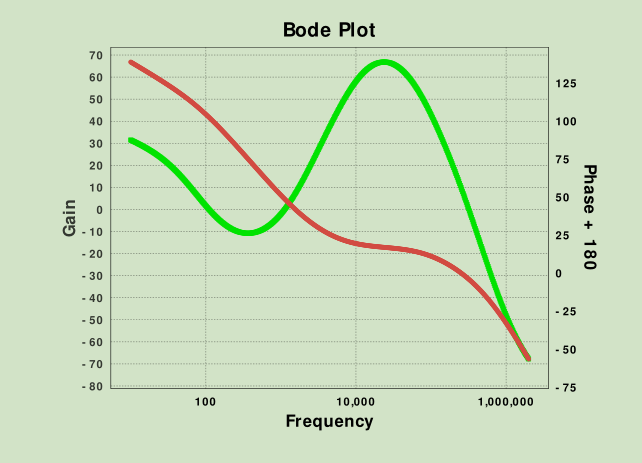

I have three questions about power stability, please help me check it.

1) Is the chip margin greater than 45 °?

2) Is the bandwidth gain less than 110Mhz?

3) Is the gain margin less than -10dB?