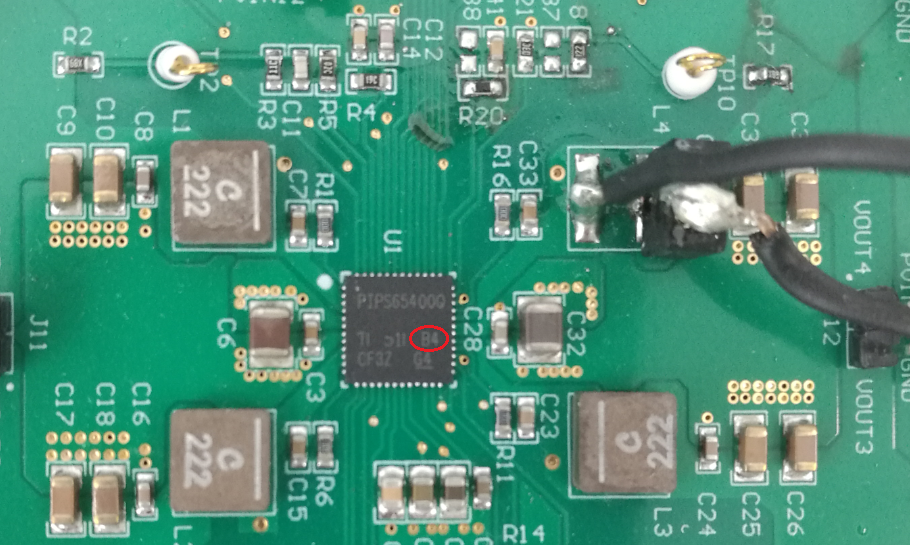

My customer is asking the following questions regarding the TPS65400 EN pins:

The data sheet indicates all ENSWx pins are ignored when the ENABLE_PIN_CONFIG field is set to 01 (Sec 8.6.2.3). However, Figure 31 does not indicate this -- because of the AND gates, the ENABLE pin must be high in order for the output to be ON according to the diagram. This is the behavior I find on the TPS65400 eval board. I cannot get the outputs to turn when the ENSWx pin is pulled low, even when ENABLE_PIN_CONFIG = 01 (inactive enable). Is this feature supported on the chip? Are there additional register settings that must be made?

The customer seems to be correct if you look at figure 31. Can you explain this?

Thanks for your help with this issue!

Richard Elmquist