Hello,

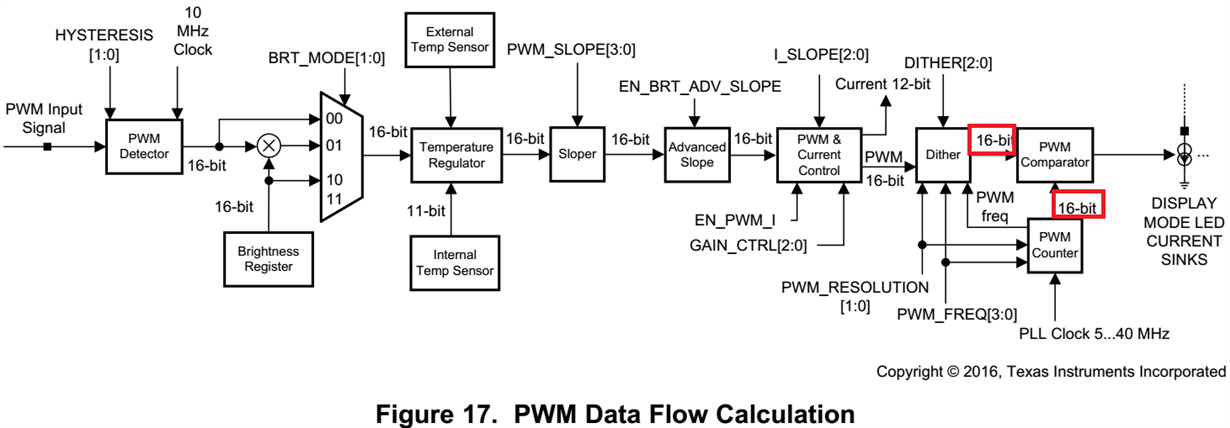

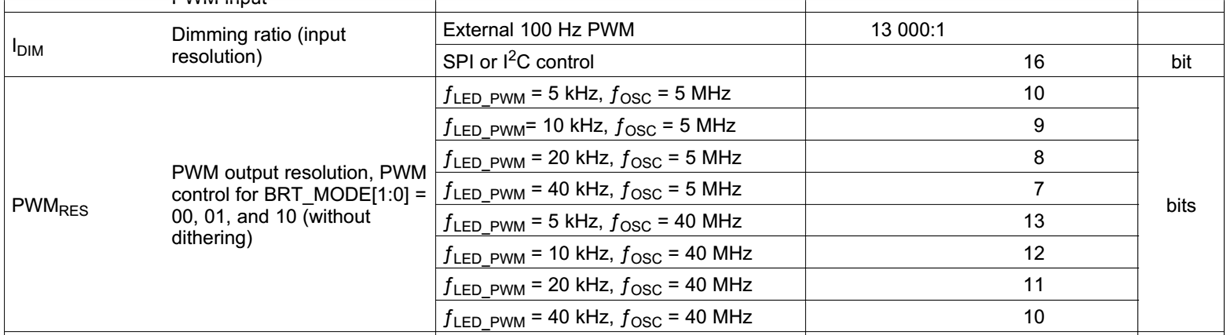

My customer would like to make sure whether Fig 17 is correct if I compare it with the specification on P9.

Fig 17 says that the 16bit resolution at the end of flow, however if I check the specifications on page 9, it seems maximum resolution is 13bit (typ).

Can you help me to understand how these numbers work?

Thank you for your support in advance.

Regards,

Ken

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.