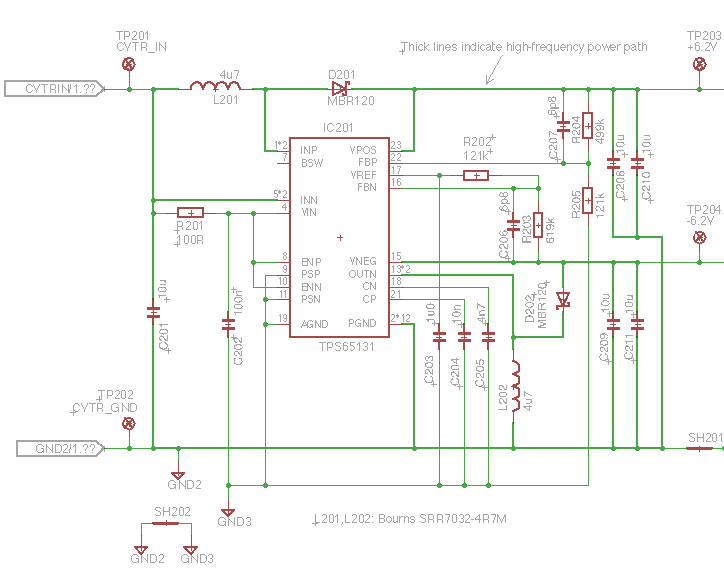

I have a 3.7V to +/-6.2V converter using a TPS65131. The circuit is essentially the same as the TPS65131EVM, with R2=121k, R5=619k, 6.8pF in || with R5. CN is 4.7nF to AGND. Vref has 1.0uF to AGND. Circuit layout is as tight as I can make it with 0603 components, on a double layer board with ground and power traces using polygons as large as possible, as much like the recommended layout as I could achieve with 0603. PSP and PSN are connected to AGND.

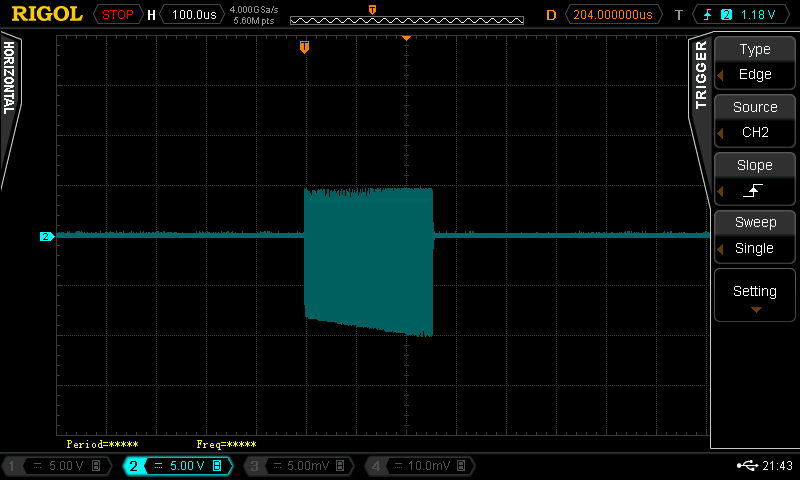

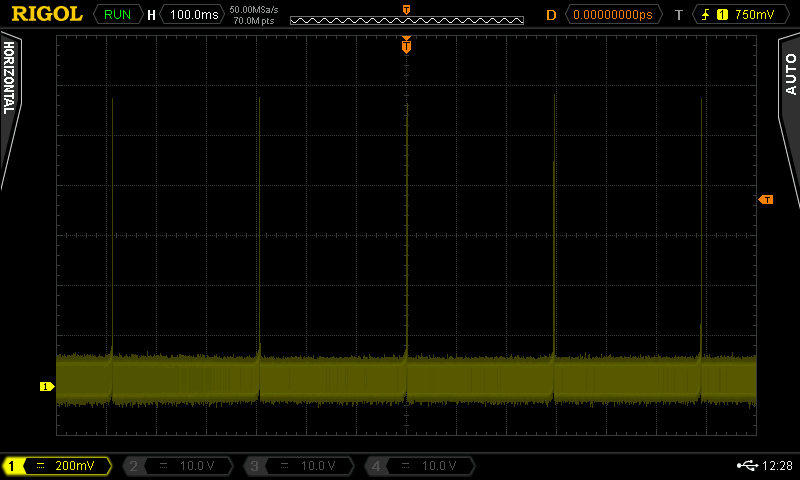

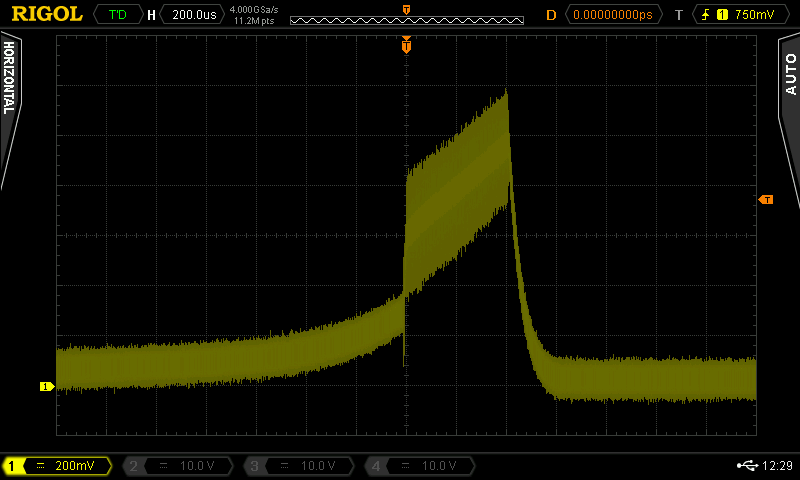

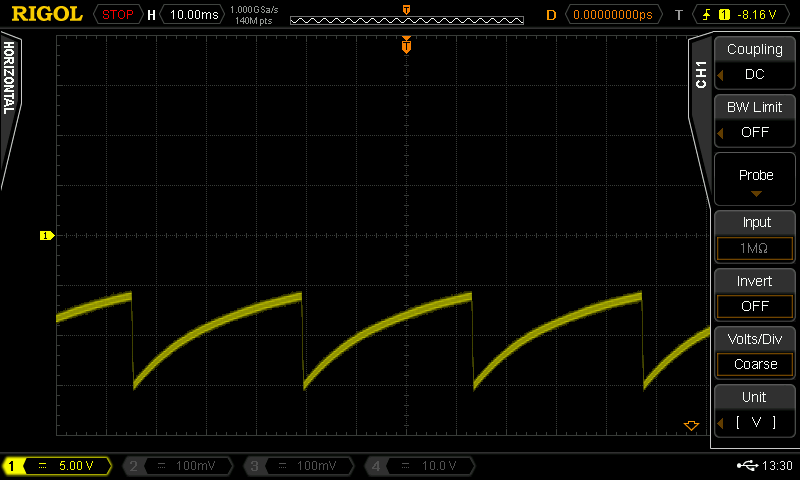

Positive rail works perfectly. At no load, negative rail works fine with 2.5V input, but with anything higher, it goes into a discontinuous bursty mode where every ~80msec it does about 250usec of ~1.4MHz rectangle wave, with the negative excursion increasing over the 250usec interval till it gets to about -10V.

The EVM with the same component values works fine; but both of my two prototype boards fail in the same way as each other. So I am assuming this is a problem with my PCB layout. But, what should I look at? Are there any experiments I can do to try to track this down?

Here's what the burst looks like:

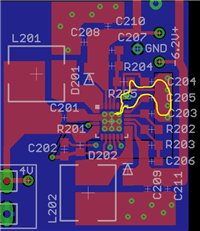

And here's the relevant part of the board layout: