Dear TI,

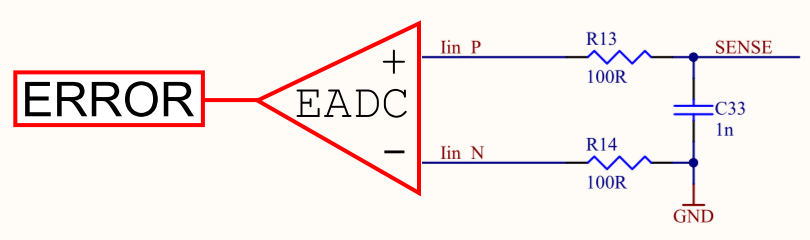

I'm developing firmware for a device based on UCD3138A. The device regulates current, so it measures voltage on a current sense resistor by means of front-end 0 (EAP0-EAN0). The current sense resistor is on low-side, so one of its terminals is connected to ground, along with EAN0.

The problem that occurs in this case is that the device behaves exactly like the current sense resistor was connected to a negative voltage instead of ground (to which it is connected).

When DAC_VALUE is set to 0, the control loop produces some high-side PWM pulses, which cause some current to flow through the load. The voltage measured on the current sense resistor is far higher (like 40x) than any voltage that would correspond to output equal to 0 of the EADC. The same voltage is applied to the input of the front-end. However, the error value reported by the device is 0, and in this state the output value of the filter is non-zero (only the integral branch is active, with KI = 1, branches P and D have their K coefficients set to 0 and are explicitly turned off in control register). The output value of the filter seems to match the observed duty cycle. When the supply voltage is varied, the duty cycle changes accordingly and the output current is kept regulated at the same (invalid) non-zero value. This means, that EADC is able to produce negative error signal to decrease the integrated filter value - but it doesn't drive that value to 0, as it should, maintaining the (invalid) regulation instead, and the error signal becomes 0 despite of high non-zero feedback. This feedback is of the order of 10mV, which should give the error value of about -10. EADC is configured in automatic gain shift mode, but it has been also tested with constant 8x gain (AFE_GAIN = 3).

Two prototypes were tested and both experience this behaviour, but with different "minimum duty cycle" - i.e. for example one device doesn't go below 15%, and the second below 10% (for the same supply voltage).

For higher output settings the devices regulate the output correctly (at least: without such unexplainable effects).

Please, help me debug the thing. What else can be checked? Are the any specific details not described in documentation?

Best regards,

Adam