Other Parts Discussed in Thread: CSD18502KCS

Hello,

The project I am working on involves using the LM25069-2 as a load protection circuit of a microcontroller. The circuit has been designed according to the recommended circuit in the datasheet. The evaluation module of the microcontroller has a total capacitance of 245 uF. When no load is connected to the output, LM25069 gives an output of 3.3V (which is the input). But on connecting the evaluation module, the output voltage drops close to zero.

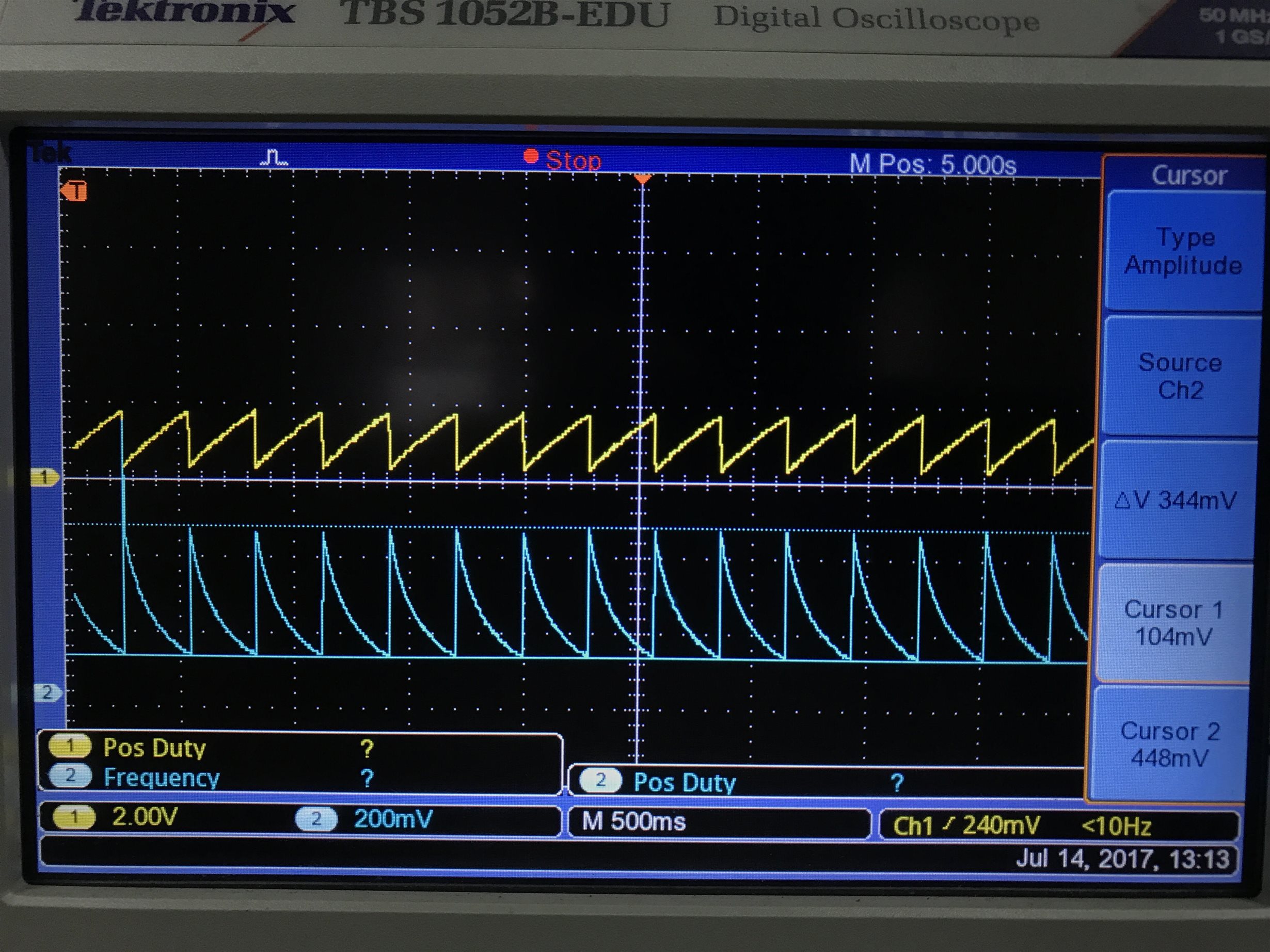

Yellow: Timing Capacitor(The rise time is 280 ms) Blue: Output (Ripple between 104 mV and 448mV). The gate pin gives a high signal during the fall time of the yellow wave (which is actually just a spike of 1.5-2V) and during the rise time it is low.

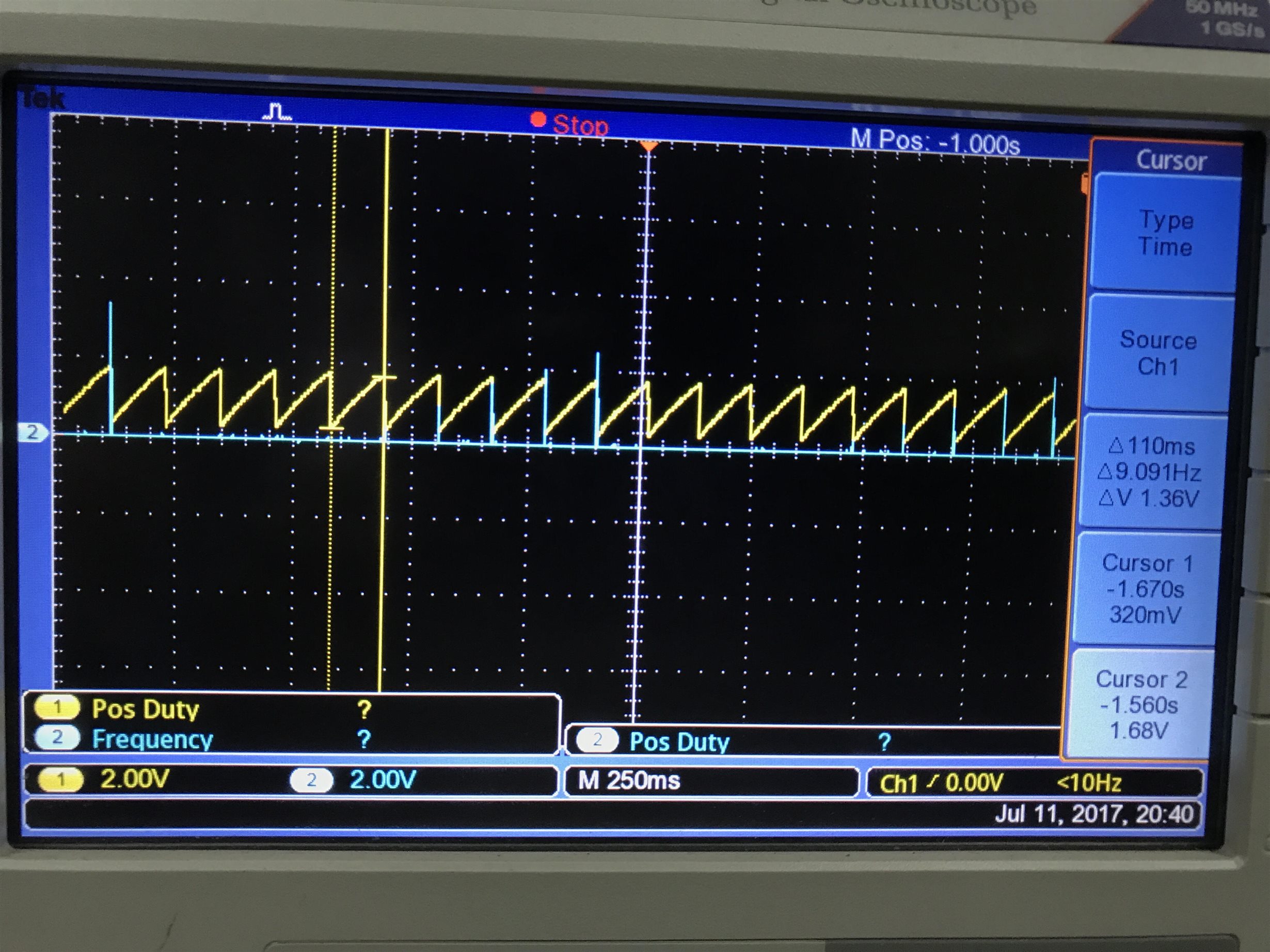

The yellow wave form goes from 0.3V to 1.72V and has a time exactly of insertion delay.

The waveform suggests a net resistance parallel to the load capacitors of about 1.8 kohm. Based on this the turn-on time was calculated to be 0.8 ms . insertion delay is 278ms. Timer pin has a capacitor of 0.89uF. Fault timeout is set at 15.8ms.

A current limit of 1A was set initially but later when the sense resistor was shorted no change was observed in the output. UVLO and OVLO are set at 2.9 and 3.5V respectively and hysteresis of both is close to 0.1V. No resistor is connected at Rpwr as that function was not needed.

I went through all the parameters in the datasheet but still can't figure out why the output is unable to rise to its normal 3.3V but couldn't find anything. Has anyone seen something similar happen? What can I do to resolve this?