Hello

I have some question for TBS7B63-Q1. I want to use it as standard watchdog mode.

1)

T(WD_TOL) is defined as +-10%. Does this value include tolerance of R(ROSC), +-1%?

2)

To clear wathdog counter(to start next OW), rising edge of WD is abolutely reqruied, isn’t it?

If the WD signal is high fixed after WD initialization, watdhdog counter is not cleared and FLT occurrs. Right?

3)

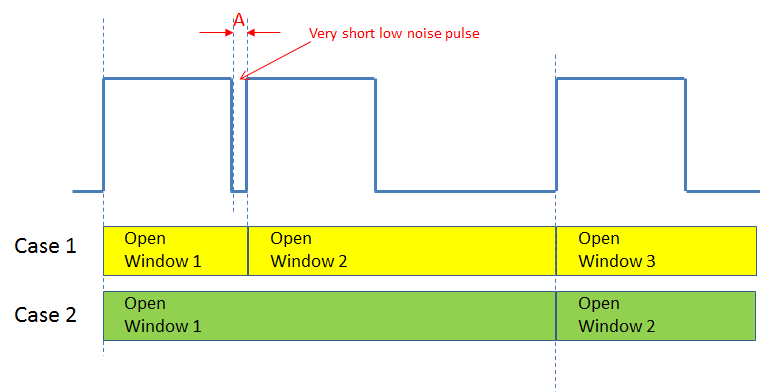

When WD signal is High and this signal goes to low for a very short time due the noise, this low signal can be detected as low siganl?

For example, in case of 100usec high à 1nsec low (noise) à High, this 1nsec low à high could be detected as correct riging edge?

4)

Could you tell me max value of EN pin input current?

Regards,

Oba