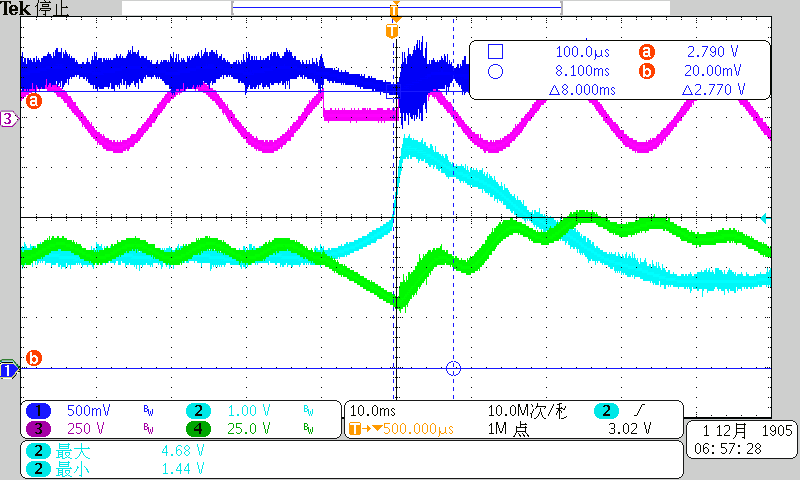

We are conducting a input voltage drop test , with input voltage power off for 10ms and then power on, when power on, the IC will reach peak current limit and protection for several periods.

This is what we think what happened: as input voltage lost, output voltage begin to decrease, when Vsense is below 2.8V, slew rate correction begin to work, 100uA current source charges VAO, VAO increases, when input powers on, current loop has a high output and cause a large duty cycle, then inductor current is charged high to reach the current limit.

Is this right? What can be done to avoid this?