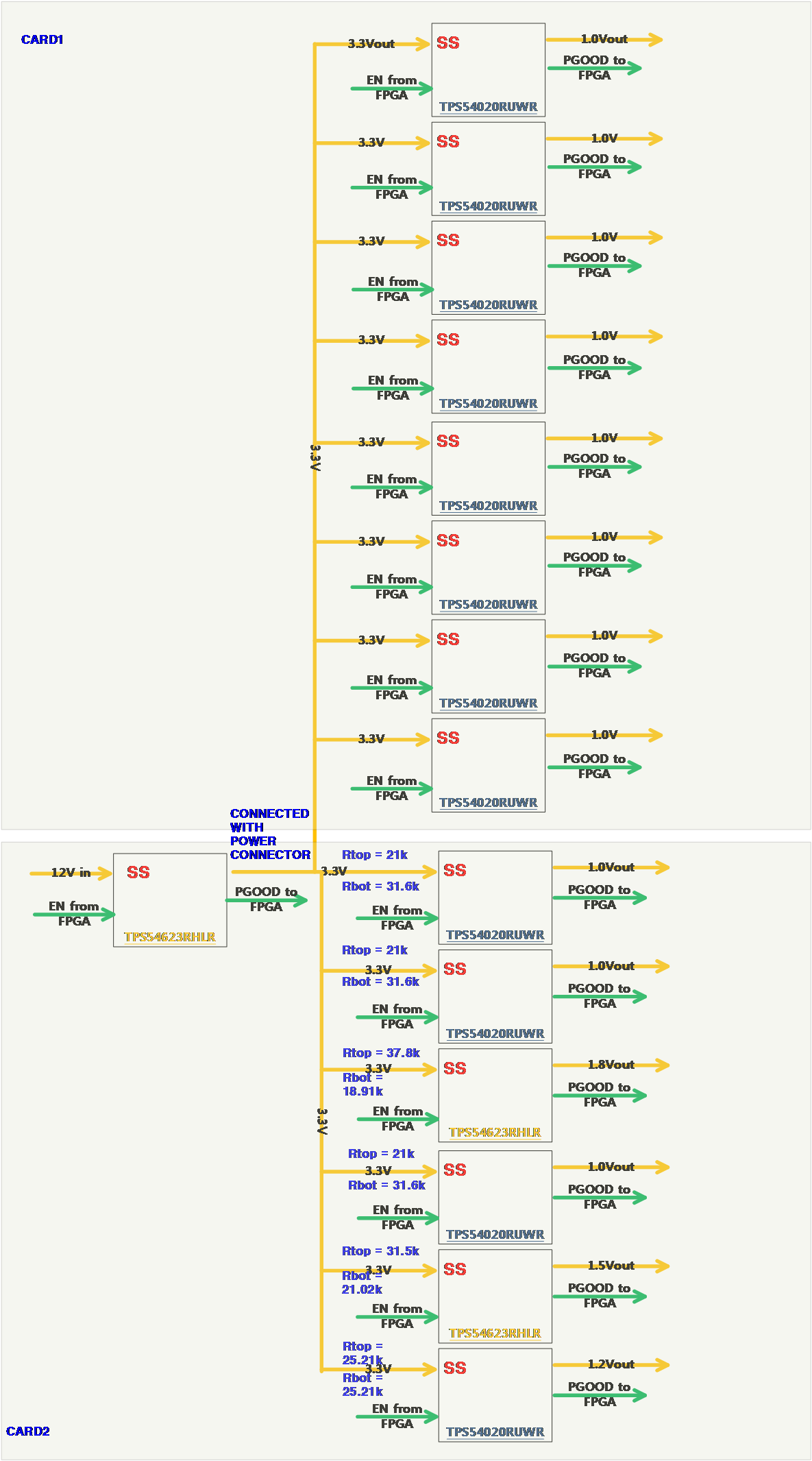

Other Parts Discussed in Thread: TPS54623,

Hello TI,

I have already asked a question in the following article, but it has become too long and I am rewriting it.

https://e2e.ti.com/support/power_management/non-isolated_dcdc/f/196/p/609676/2270102#2270102

In sum, yy question is below two now.

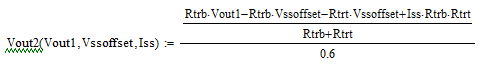

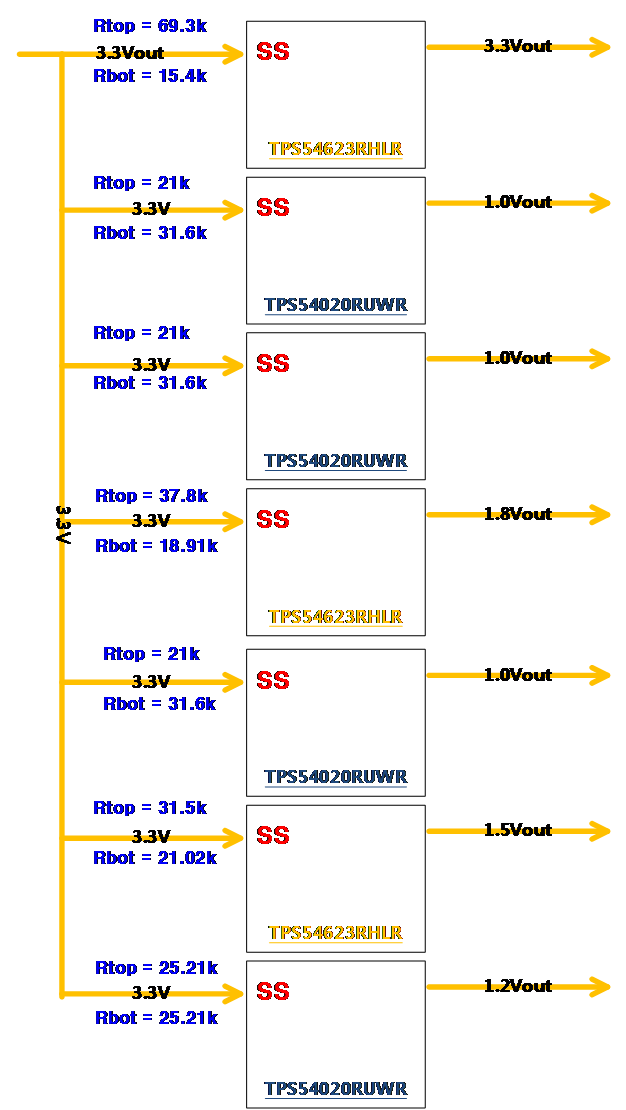

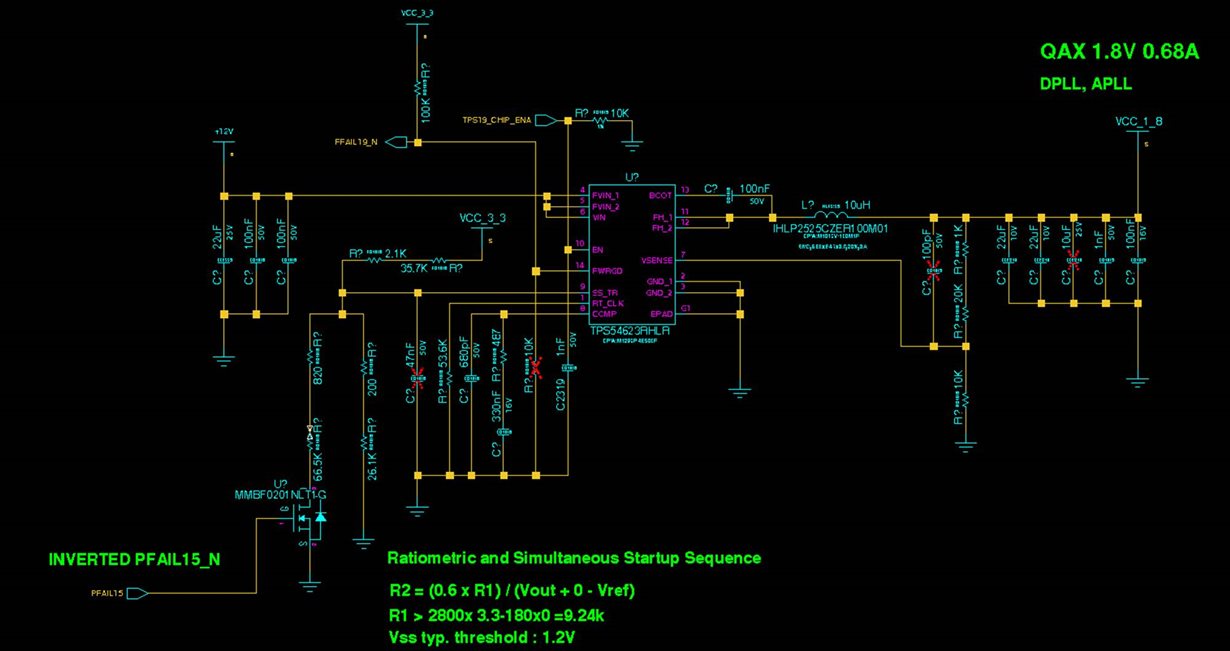

1. Please review and confirm our schematic.

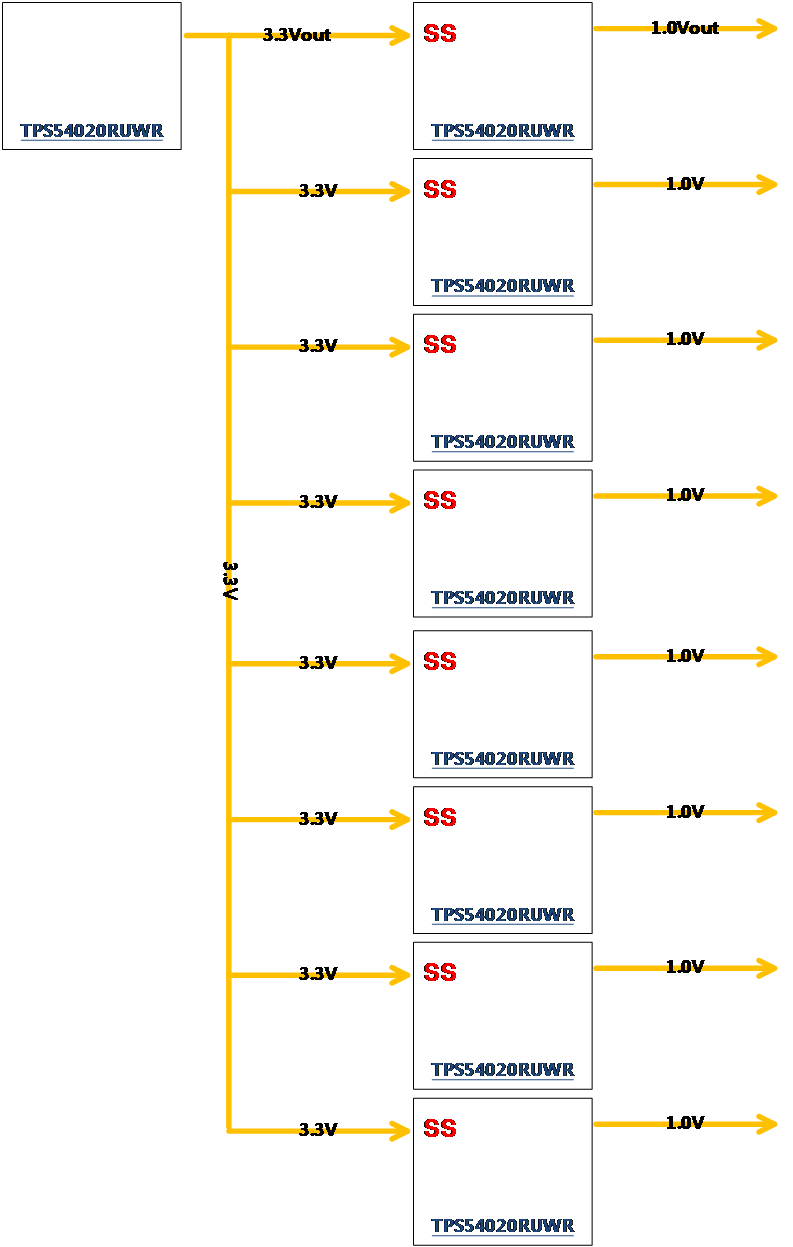

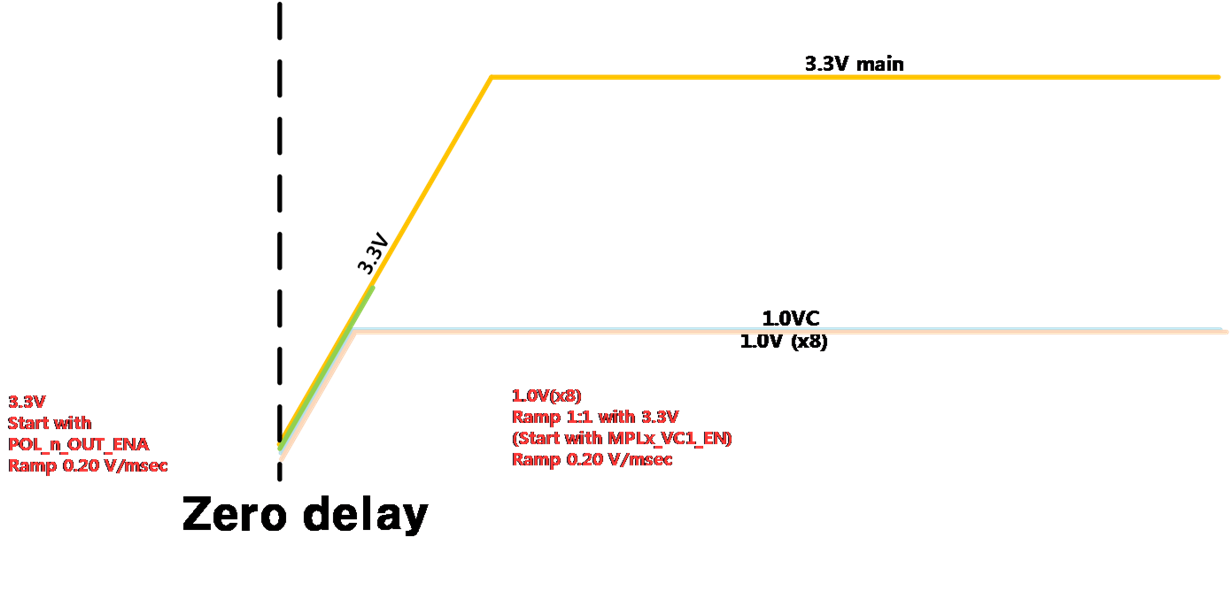

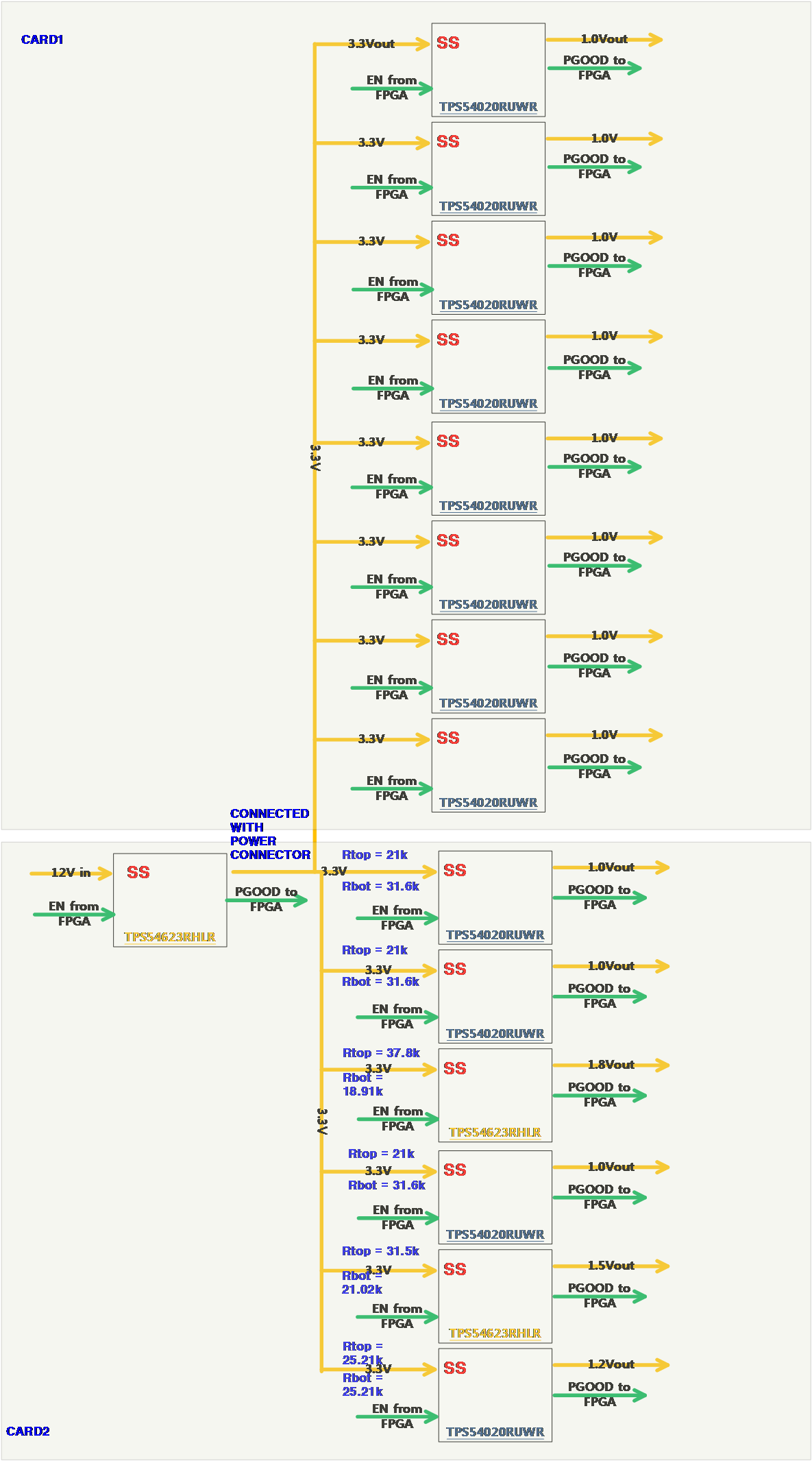

2. Is it possible to design with following structure? (8 parellel TPS54020s)

thanks,

TS