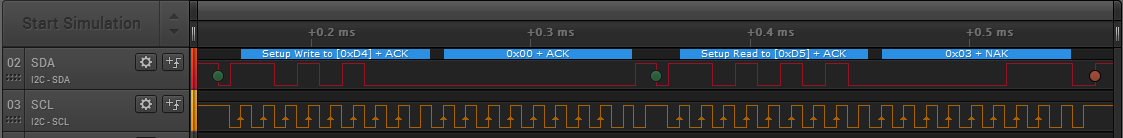

The datasheet describes the I2C protocol (i.e. start / address / data / stop, etc) but does not inform of the specific read write to access specific registers on the device.

Do I take it that to read / write specific registers the correct transfer protocol uses the combined format (as described in the I2C spec) with a second byte being written (after the device's bus address) as a register offset and then consecutive read and write bytes in the transfer reading from / writing to consecutive register addresses after this offset? Or do I need to address each register individually?