Other Parts Discussed in Thread: TLVH431, TR100

Hi,

Our customer system is using TPS650250 PMIC with AM335x.

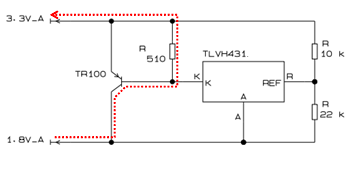

The Clamping Circuit is also used as per the suggestion in the manual (SLVU731A).

But, there is an issue in power-up sequence after adding this Clamping Circuit.

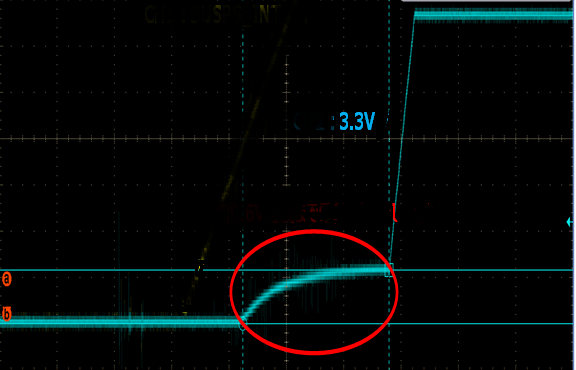

During power up, after the 1.8V line is powered up, there is a short voltage(0.6V)

induced into the 3.3V before 3.3V line is powered up as shown below.

Please let us know is this a problem in the recommended circuit

and will there be any issue on the power up sequence.

Best Regards

Kummi.