I would appreciate some advise on the soft startup and avoiding over current tripping the startup.

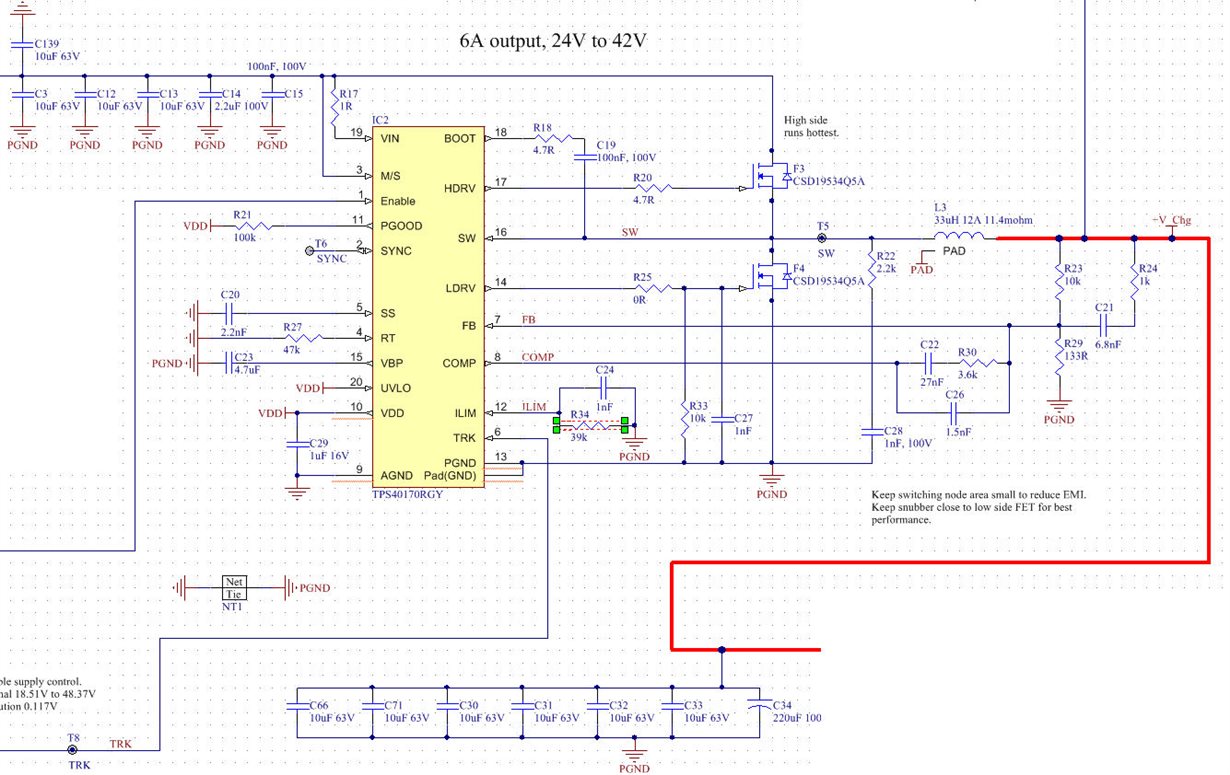

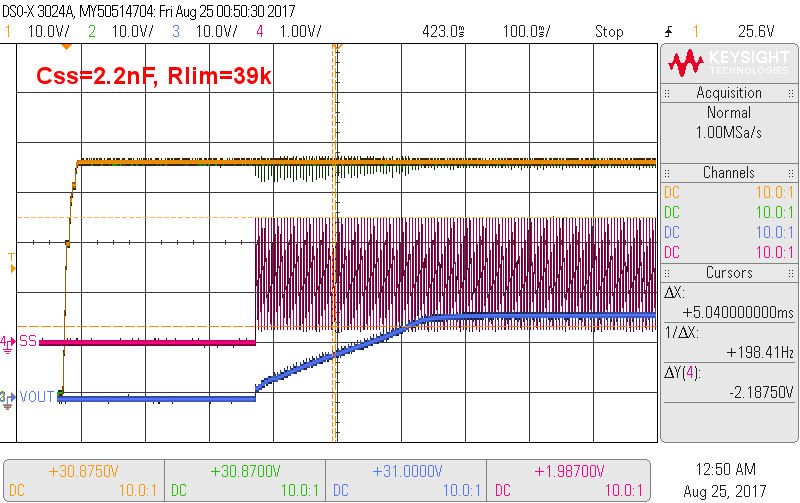

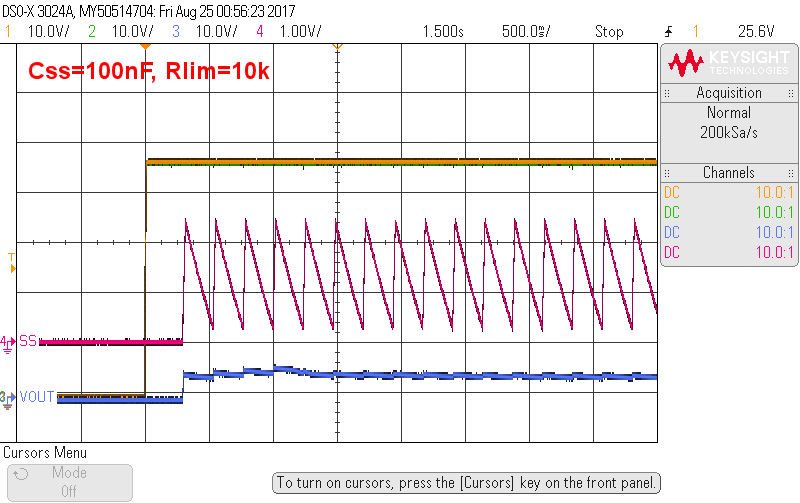

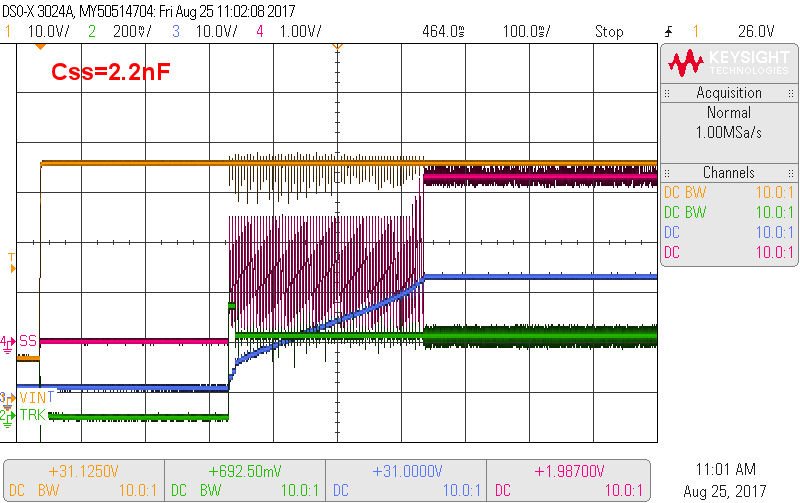

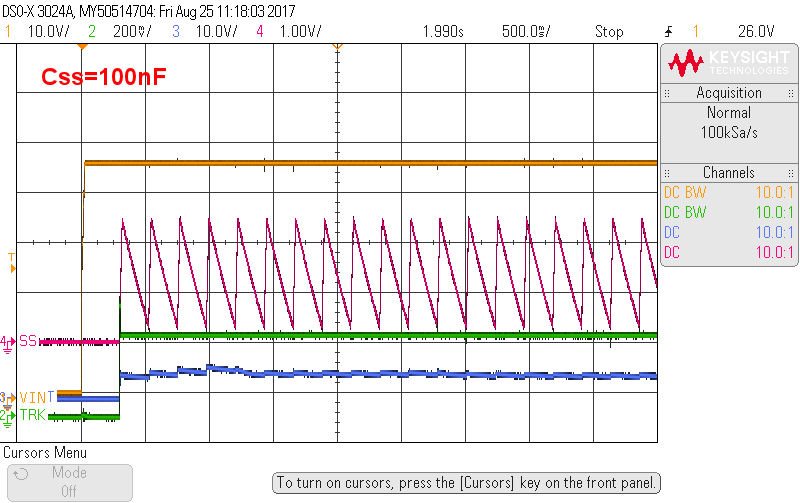

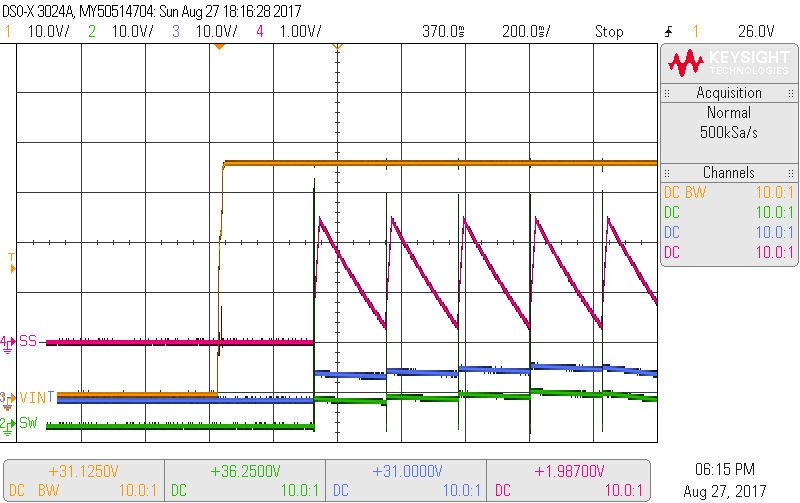

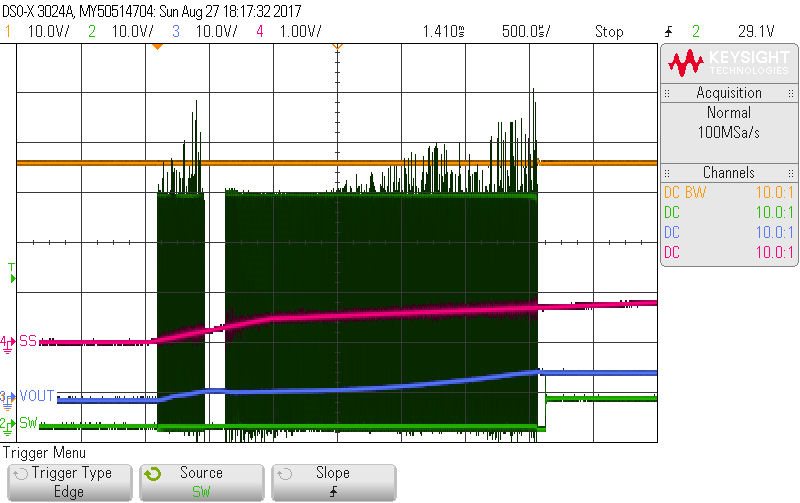

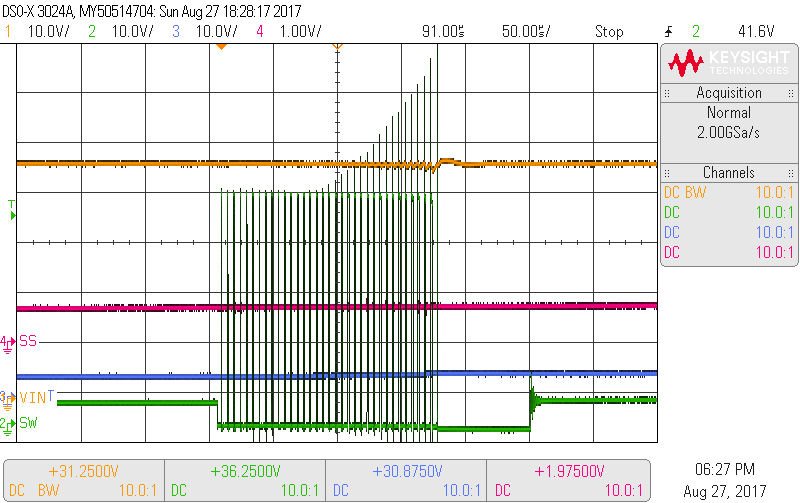

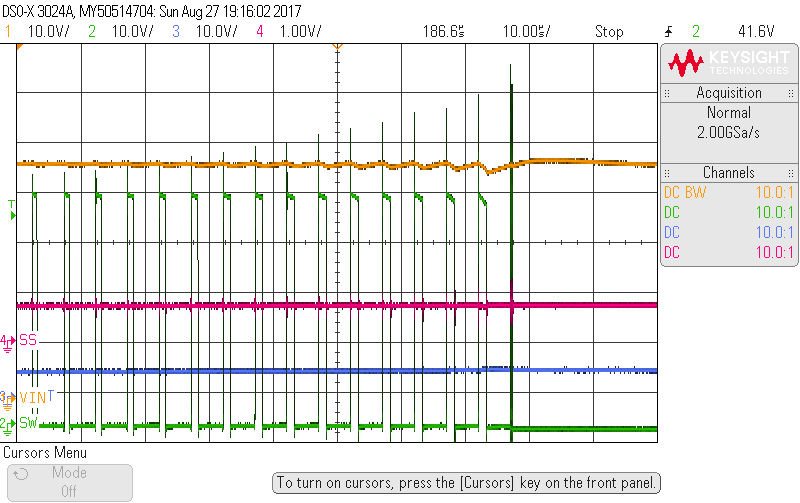

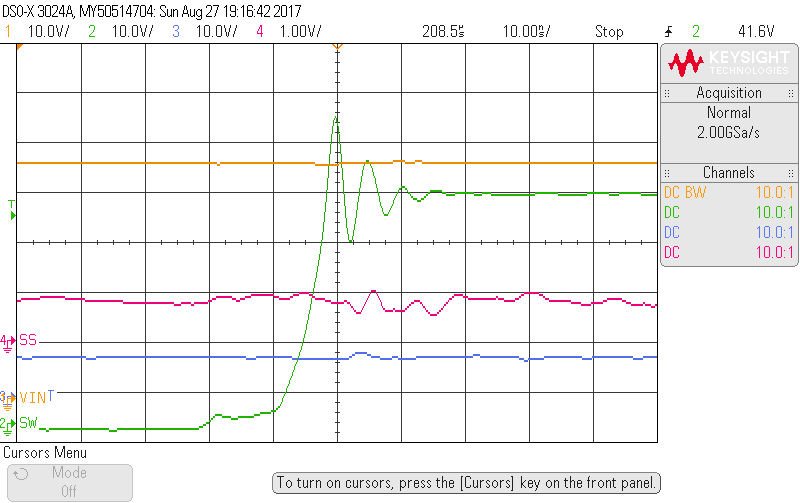

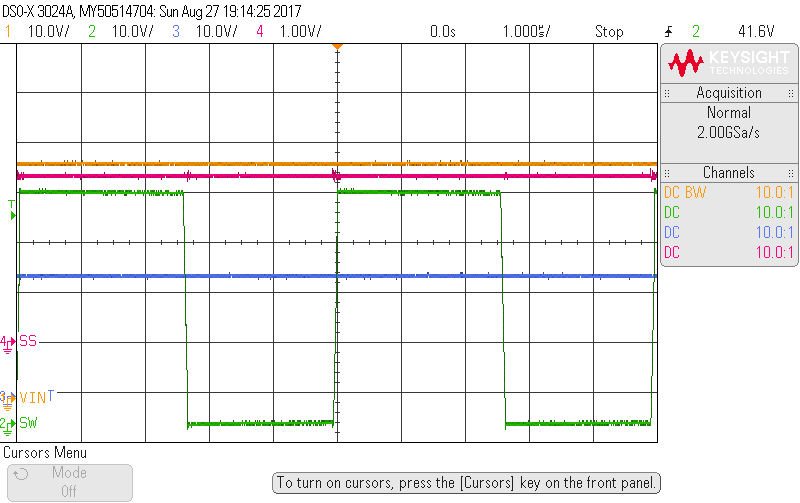

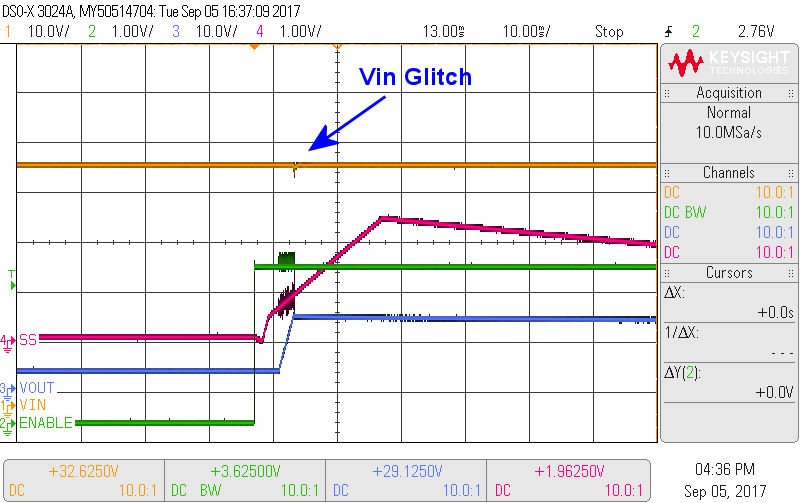

Webench recommends and Rlim=39k and Css=2.2nF, however the startup time is very short and buzzing the capacitors with repetitive inrush current re-starts. I want to target at least 100nF for Css, however the regulator will not start even at 10nF. It will start at 2.2nF, however without a load connected. 100mA load will prevent startup.

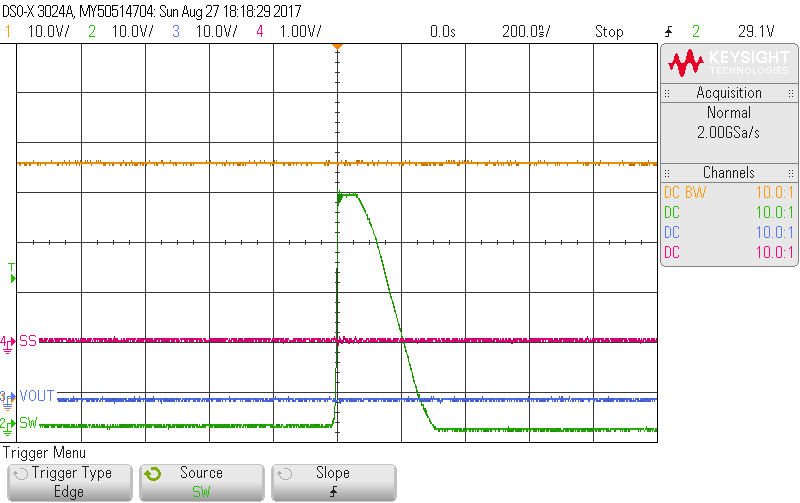

Scoping with 200MHz probe/BW and probe ring local grounded, the SW node and both gates are very clean, <1V ringing. VIN, VBP, VDD, TRK all stable and no notable noise during startup. Enable goes high when input is already stable at 48V. Once started, it runs >94% efficiency with 48V input, with 19V output/5A load.

I would like to achieve a softer startup, capable of startup with load. Would appreciate some input!