Other Parts Discussed in Thread: TPS22990, TPS22975

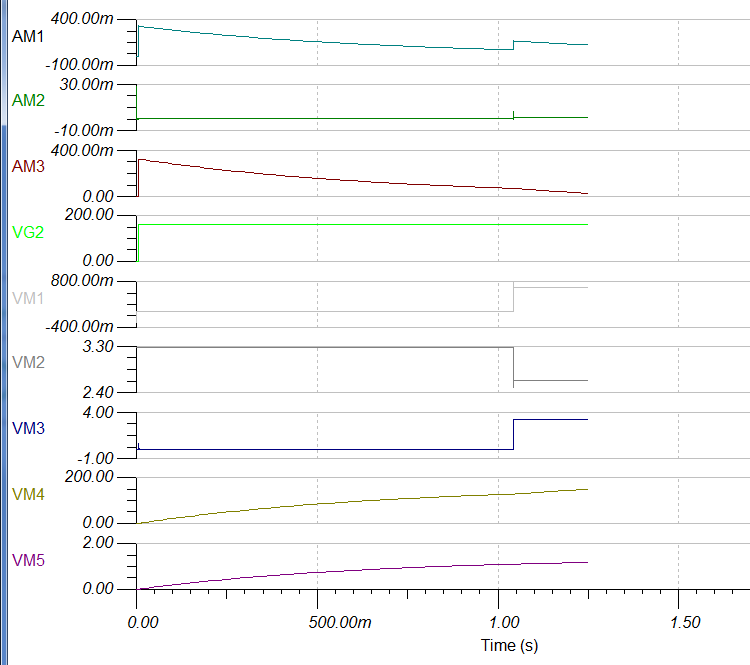

A similar more robust NFET circuit in Tina transient analysis shows very little inrush current vectors through DS in all transient modes, 470k resistive load tests. The ideal circuit uses an ICL (R4) across NFET and delays gate turn on for 1-1.5 seconds until C3,C4 caps are just above mid supply, ergo (90-163v). NFET directly replaces a bulky relay NO contacts bypass ground across ICL where the TPS output voltage slope control could perhaps remove the need for the ICL.

The ICL now remains reactive across on state NFET and ensures transient reverse currents from ground up to 40 amps are controlled. It doesn't seem plausible 40 amps or any current above a few capacitive ripple current amps or (dv/dt) would ever occur unless an HV caps suddenly shorts out. Transient analysis shows less than 700ma inrush current with 250/500 ohm resistor across the NFET DS when 163v is suddenly switched on.

Will dv/dt jotting below -0.3v destroy the TPS22969 NFET if the output (source) is tied to ground and the input (drain) faces the load? Secondly is there a Tina Macro available to simulate circuit operation?

Thanks for effort!