Champs,

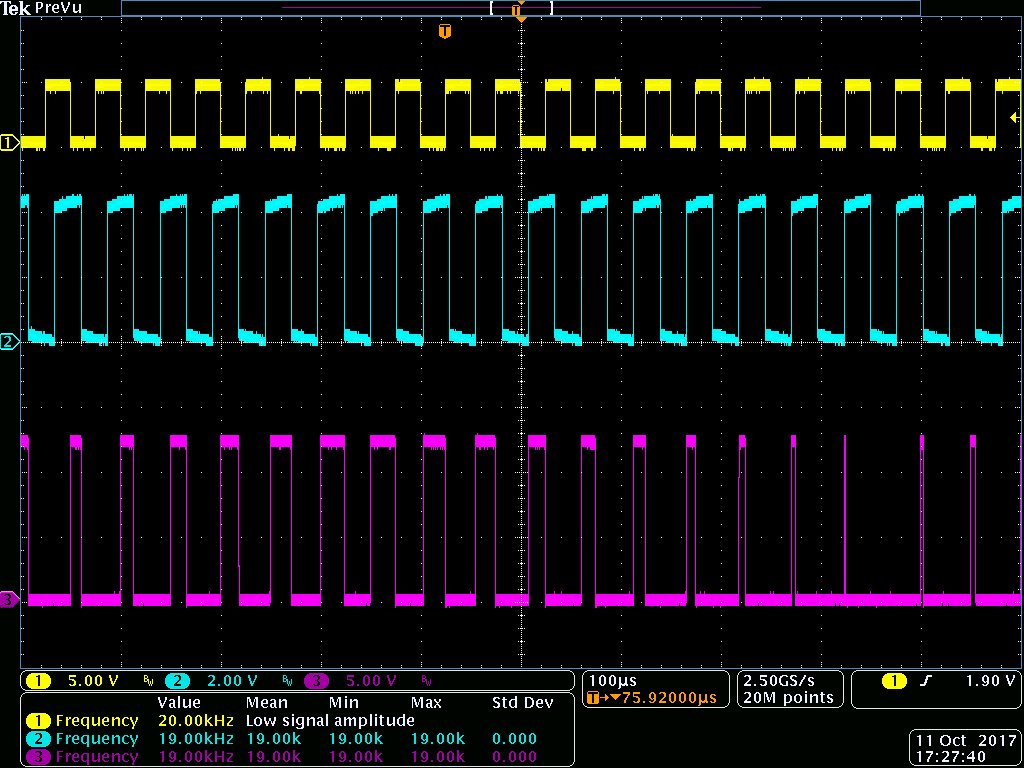

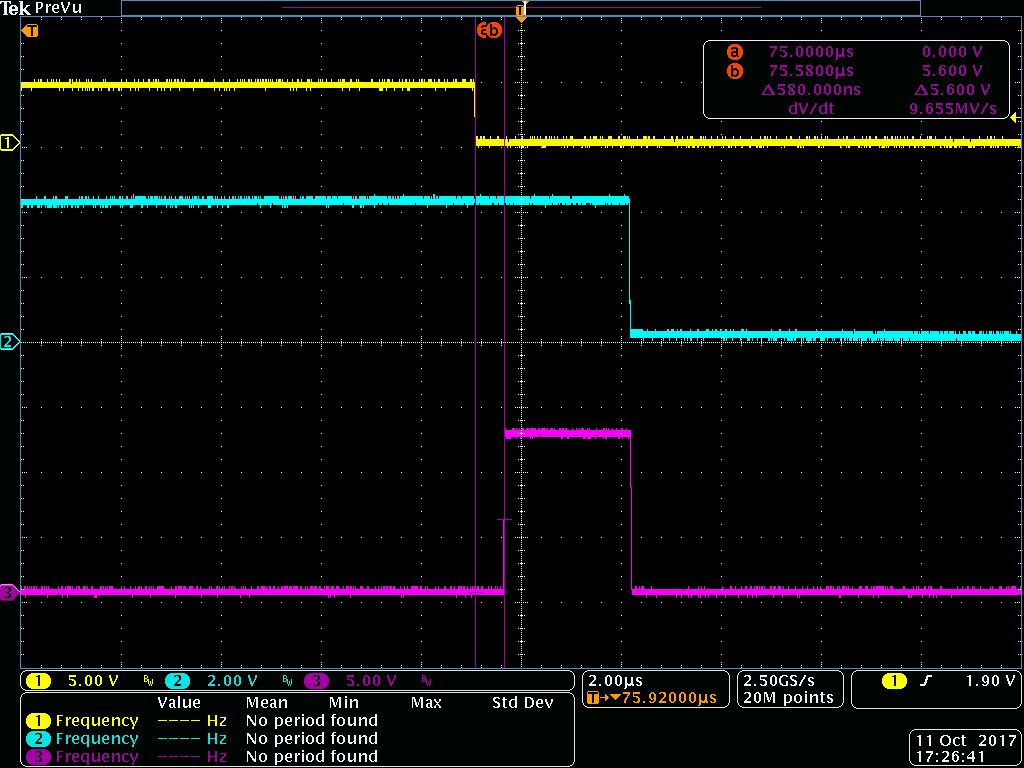

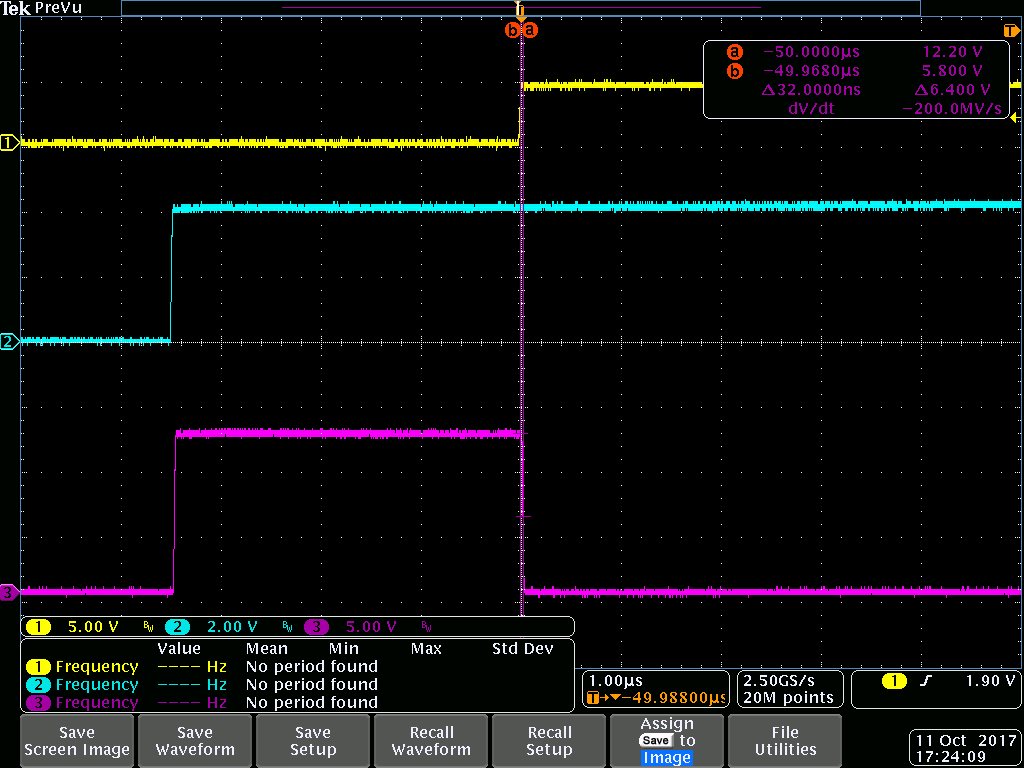

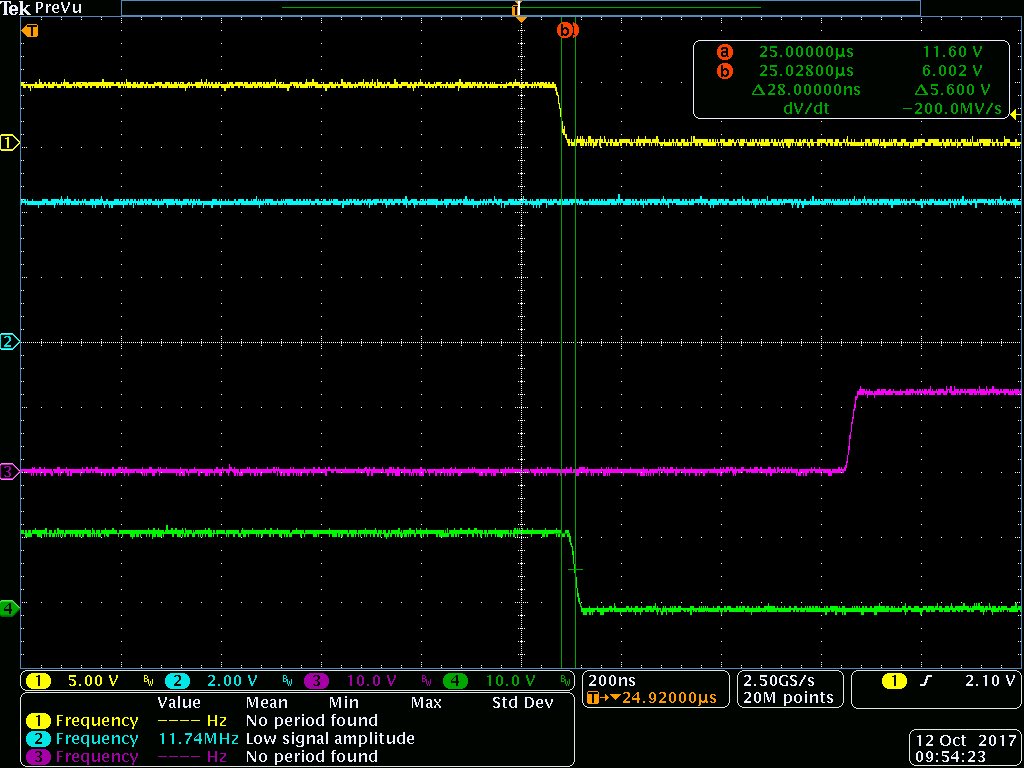

So a question on the EN pin... FUNCTIONALLY it looks like it's just an AND gate to the drivers... but the level shift on the high side and the programmable dead time function has me concerned. Can the EN pin support a rapidly toggling signal unrelated to/out of phase with the signal at the IN pin? Or is it intended more as long-term shutdown function that could glitch if given a rapidly toggling signal? A worst-case example of what I mean would be to input 20 kHz to the IN pin and 19 kHz into the EN pin. Would the 5106 handle this gracefully?