Dear, All

The customer is using TPS 65910AA1.

In their system, a phenomenon occurred in which the microcontroller did not start once about every ten times.

At that time, the TPS65910 is not outputting power other than VRTC.

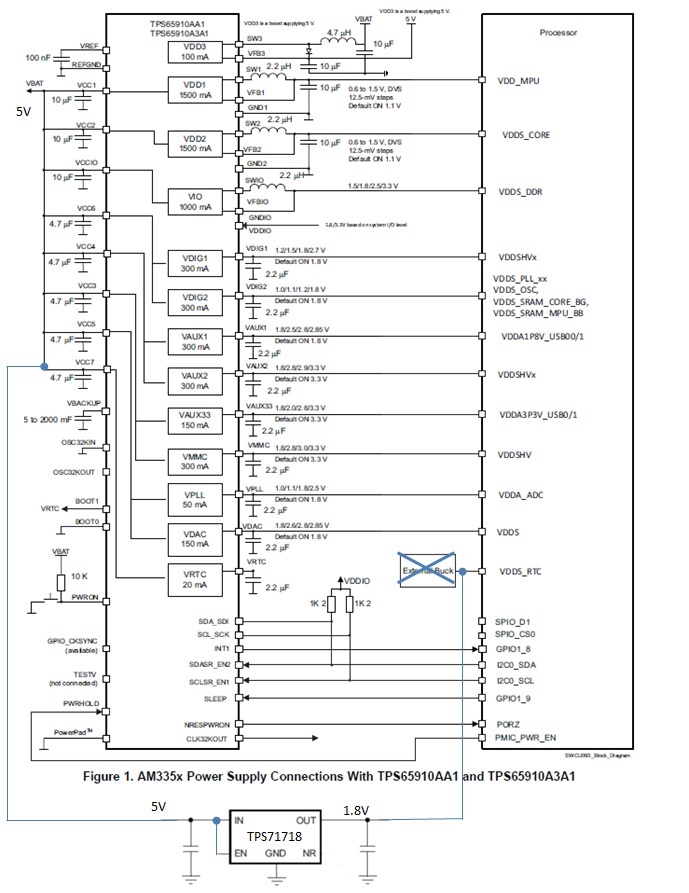

The circuit configuration is shown below.

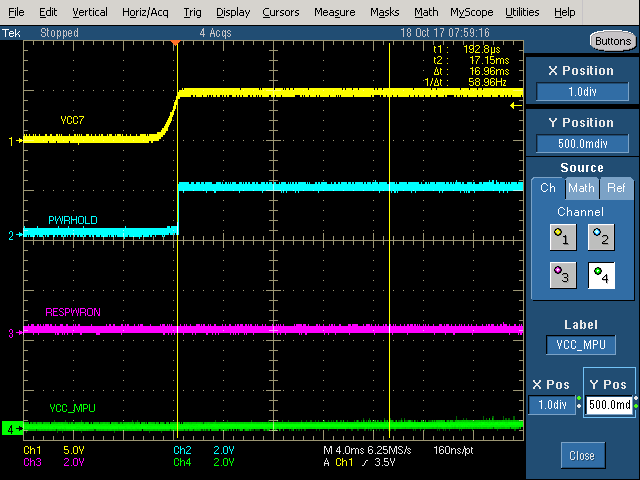

After confirming the waveform, PWRHOLD was 'High' at the timing when the 5V power supply rose to about 2.8V.

For that reason they suspect that the timing to make PWRHOLD 'High' need some time from the 5V rise.

It is stated in the data sheet of TPS65910 that the 5V input is judged within the voltage range of 2.5V to 3V.

Please tell me how long it is while turning on PWRHOLD after 5V voltage reaches 3V.

Thanks, Masami M.