Other Parts Discussed in Thread: TIDA-00778

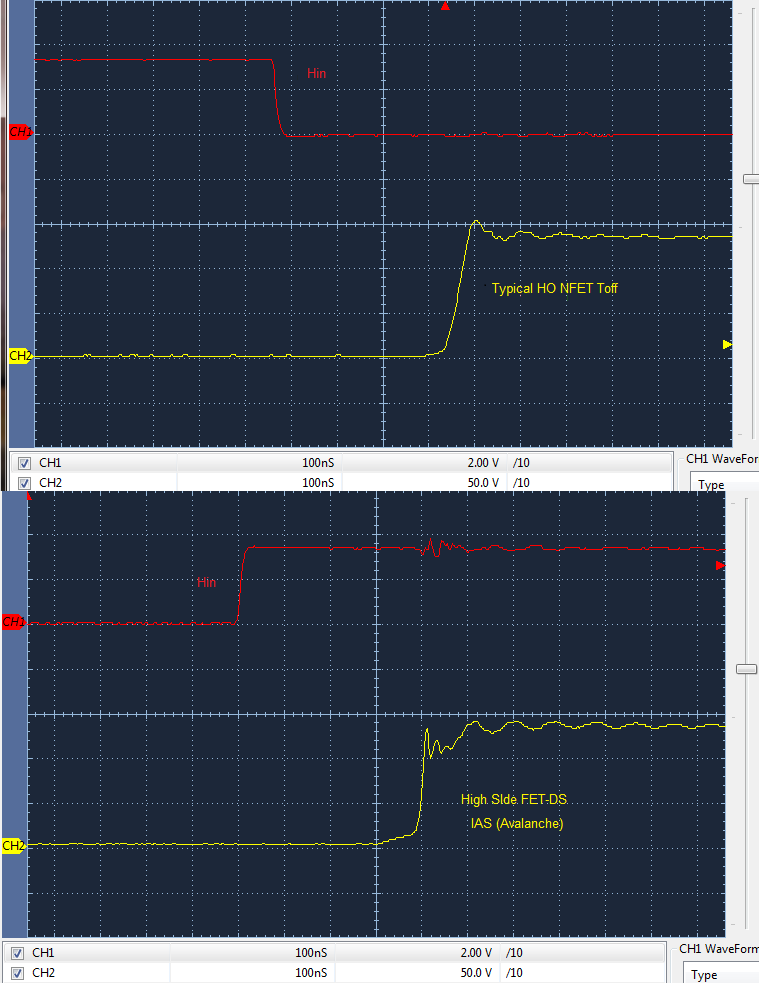

Finding the datasheet is not so clear in describing IGPK+ for conditions of 3v3 GPIO driving HI/LI and what is less than 10us PW relatively mean?

And 100ns = 10Mhz PWM frequency as described AMR Iout [Output current, HO, LO, IOUT_PULSED (100 ns) +/- 4A ]

If <10us PW = <100kHz can the IGPK+ 4 amps be produced with say a 50-80us HO/LO Ton PW driven by 12.5kHz to 20kHz PWM period?

Using the less than symbol to describe IGPK+ might be taken to mean a shorter PW as in nanoseconds or might even infer PW under 100kHz relative to the PWM frequency of the HI/LI inputs. For example a 10us PW would not be considered less then a 10ns PW and much shorter or (<) 10us PW yet produces a much faster or (>) frequency. Seemingly the IGPK+ modulated PWM test conditions need to be disclosed in DS in order that IGPK+ of <10us PW has any relative meaning to HI/LI input of PWM frequency.

Does IGPK+ PW <10us period infer 1us, 5us, .5us or perhaps 11us up to 100ns relative to HI/LI driving PWM frequency?