Hello,

Is there a predictable maximum delay time between the PMBus CONTROL pin being pulled low and the first EN in sequence being de-asserted?

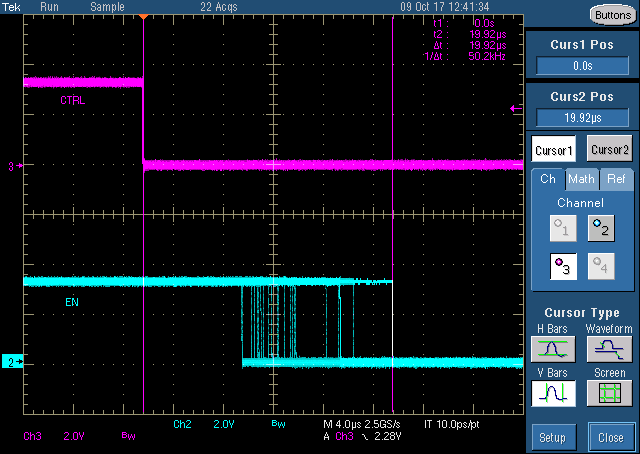

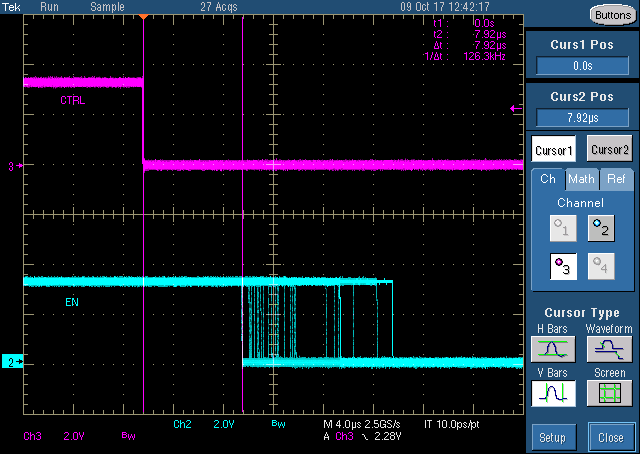

I checked on the bench using the UCD90320EVM-783 and manually toggling CTRL in the Fusion GUI, and observed delays from 8 us to 20 us across ~20 attempts. In my application, I need this value to be <= 100 us.

If the CTRL pin can't give me <= 100 us delay time, is there a GPI that is faster that would?

Thanks,

Jonathan